IFT1227 Architecture des

ordinateurs I

Hiver 2006

Devoir 1

Par groupe 2.

Tout plagiat sera

sanctionné selon les règlements de la faculté

Date de

remise : vendredi 17 février 2006, 10h30 à votre démonstrateur.

Question 1

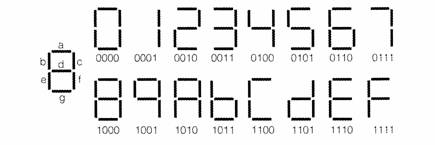

Les affichages d’une sortie à 7-segments, comme les chiffres des calculatrices, sont décrites dans la figure suivante. Les sept segments sont numérotés de a à g. Dessiner un circuit qui prend en entrée un nombre binaire de 4-bits et produit en sortie le signal de contrôle pour le segment g seulement. Un 0 en sortie éteint le segment correspondant, et un 1 en sortie allume le segment correspondant. Montrer la table de vérité et une implémentation qui utilise uniquement un MUX. Étiqueter chaque ligne du MUX par sa valeur.

Question 2

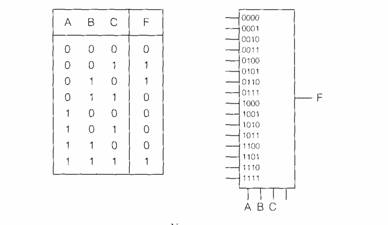

Implémenter la fonction F décrite par la table de vérité suivante, en utilisant le MUX 16-à-1 ci-dessous. Étiqueter toutes les lignes par leur valeur y compris la ligne de contrôle qui ne l’est pas encore.

Question 3

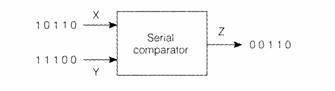

Dessiner une machine à états finis qui prend en entrées deux mots binaire X et Y en série, le bit de poids faible en premier, et qui produit comme sortie un bit Z qui est vrai si X > Y et faux si X ≤ Y. On suppose qu’à l’initialisation de la machine, X = Y. Ceci veut dire que la sortie Z est fausse jusqu’à ce que X > Y. Le schéma suivant montre un exemple de séquences d’entrées et la séquence de sortie correspondance.

Question 4

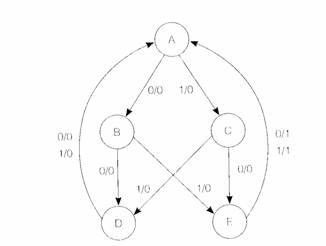

Dessiner un circuit logique en utilisant des bascules D ainsi que des portes logiques ET, OU, NON qui correspond à une réalisation de la machine à états finis suivante :

Il faudra établir la table de vérité de chaque sortie ainsi que de chaque bit d’état. Il faudra aussi donner leur expression algébrique sous forme de somme de produits.