# **Private vs. Shared Data**

SMP must support both

### □ Private

normal cache policies and benefits

# □ Shared

- simplifies communication between the multiple processors

- simple reads and writes to memory

- · obvious synchronization requirement however

- introduces consistency & coherence problems

- · shared data may be replicated in the multiple caches

- in order to preserve uniprocessor (sequential consistency) semantics all copies must be identical

- · writes are clearly the source of potential confusion

- · consider the drawbacks of conventional cache wisdom

- write-back, large block/line sizes, tag bit semantics problems?

3

• write-buffers - problems?

University of Utah

# **Consistency and Coherence**

- □ Informal coherence model

- any read of a data item should return the value that was most recently written

- · appealing but way too simple in the SMP world

# □ Simple model contains 2 behavioral aspects

- coherence

- defines *what* value is returned by a read

- consistency

- defines when a written value will be returned by a read

- · this is a problem since a write at processor 1 may have happened but still not have left the processor by the time a read at processor 2 happens

- · note that this when problem gets more difficult as the physical extent of the multiprocessor system increases

- both critical to writing correct shared memory programs

4

### **Coherence**

A memory system is coherent if:

given no other writes, a processor P will get its last written value to X on a read of X

- simply preserves program order and is the normal expectation

- given no other writes, a read by P1 of X gets the value written

- by P2 if the read and write are *sufficiently* separated

- we'll defer the issue of what *sufficient* means and how it is controlled for now

- writes to the same location are serialized

- · fundamental need to avoid the concurrent writer problem

#### □ Implication

- reordering reads is OK

- · similar to uniprocessor world

- writes must finish in program order (write serialization)

- · definitely not the same as in the uniprocessor world

- · this restriction will be relaxed later

|   | University of Utah  |

|---|---------------------|

| V | School of Computing |

5

CS6810

# **Enforcing Coherence**

#### 2 common styles

### □ Directory Based

- keep sharing and block status in a directory

- · directory may be centralized or distributed

- appropriate for DSM

### □ Snooping

- appropriate for SMP's (our focus for today)

- · take advantage of the common connection to the bus

- caches monitor transactions on the bus

- · see writes to shared data

- · modify contents of their copy if they have one

- what options are there for modifications??

- what are the costs of this approach?

University of Utah School of Computing

CS6810

# **Protocols**

#### 2 common choices

# □ Write-invalidate

- writer needs to get exclusive copy

- write forces other copies to be invalidated

- subsequent reads get new copy from the writer

- what state change is required for the writer's copy

- if 2 writers then one wins the race

- removing races requires some form of synchronization

- in single bus case we get it by default e.g. via bus arbitration

### □ Write-update

broadcast writes on bus - snoopers update blocks if they have a copy

· knowing which lines are shared helps minimize bus contention

7

how do we deal with the multiple writer race?

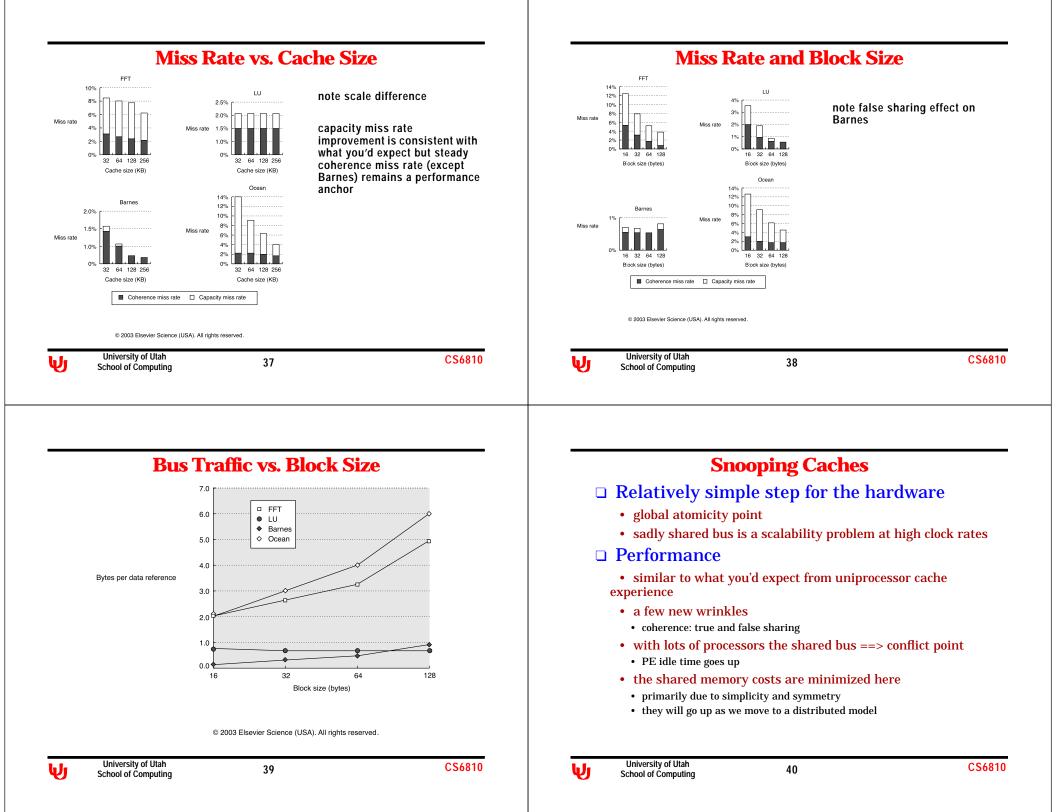

# **Performance Issues**

6

#### 3 characteristic differences

### □ Multiple writes to the same word

- less bus traffic in invalidate

- · first write causes a transaction with invalidate

- · every write causes a transaction with update

# □ Multiple word cache blocks

- same issue but applied at block granularity

- invalidate = 1 bus transaction per line per new writer

- update = 1 bus transaction for every write

#### □ Reading a remotely written value

update wins here since it has a local copy

#### Result

- · bus bandwidth issues are critical hence most common winner is invalidate

- OK for small way SMP (still true when CPU's get faster?)

8

· does every line need to use the same protocol?

# **Cache Implementation**

□ Single cache

- each line has a state: invalid, valid, dirty, etc. (status tags)

- · processor generates read and write transactions

- controller

- reacts to processor transactions

- matches address tags to determine hit or miss

- on a hit: modifies the state of the line as needed (finite state machine model)

- generates bus transactions to main memory: read or write

### □ Snooping coherent cache

- similar game but with multiple distributed controllers

- plus a new source of transactions

- controllers must watch the bus as well as the processor

- any potential problems w/ this dual master situation?

| հե | University of Utah  |

|----|---------------------|

| U. | School of Computing |

9

CS6810

# Consistency

# □ Sequential consistency

#### • Lamport's 1979 definition

- SC if the result of any execution is the same as if the operations were executed in some sequential order ...

- really is saying that the multiple total orders of all threads/programs can be arbitrarily interleaved

- one interleaved order must be the one observed

### □ Sufficient conditions

- every process issues memory requests in program order

- after a write the issuing process waits until the write is complete before proceeding

- after a read, the issuing process waits for the read to complete

- implies that previous write to this location must also complete to all processors

11

• this write atomicity can be quite demanding in modern processors where out of order and speculative everything is the norm

# **Simple Example**

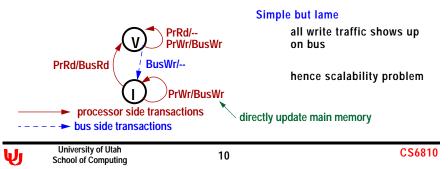

#### write-through no-allocate write-invalidate coherence

#### □ Basics

- Processor read and write ::= PrRd & PrWr transactions

- Bus read and write: BusRd & BusWr

- Line state I or V

- write-through implies all writes are seen by the memory & other processors

- hence no dirty state is necessary

# **Snooping Protocol Design Space**

### □ The Beauty

- single bus owner and snooping broadcast used to enforce write atomicity

- only a small amout of additional effort is required to permit multiprocessor cache coherent operation

### □ and The Beast

- · bus design is now critical

- · must support some additional transactions

- cache controller has dual masters

- contention possibility may require *I'm not ready* signals

- e.g. bus and CPU try for the same line tag and line contention

- new cache states will be necessary for example

- exclusive: owner (OK to write) but currently clean

- dirty: owner (OK to write) but must respond to reads by other processors

- many actual options

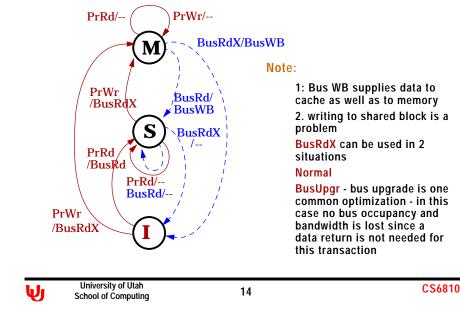

## **MSI Protocol**

write-invalidate write-back

- □ Line states: Invalid, Shared, Modified

- □ Processor transactions: PrRd, PrWr

- □ Bus transactions

- BusRd asks for a copy of the line with no intent to modify

- generated as a result of a PrRd miss

- line may be supplied by another cache or by the main memory

- BusRdX asks for an exclusive copy of the line

- generated as a result of a PrWr miss

- or from a PrWr hit on a line that is not in the M state

- note new bus transaction that is imposed by the need for cache coherence

- BusWB writeback or flush

- imposed by the write-back cache policy

- a minor extension to the BusWr idea but for lines rather than smaller data chunk size

```

University of Utah

School of Computing

```

13

CS6810

# MSI State Diagram

# **MSI Analysis**

# □ SC

- write completion is detected when BusRdX is seen on the bus

- and the data return is interned in the cache and the pending write is issued

- bus ownership guarantees atomicity

- but note the possible delayed data return to an immediate next BusRdX

### **Options**

- BusRd from M goes to S

- could also have gone to I (choice for the Synapse machine) = migratory

- tradeoff

University of Utah

School of Computing

- if new processor is likely to write soon then going to I is better

- if old processor is likely to read again soon then going to M is better

- hybrid is possible based on a protocol bit

- Sequent Symmetry Model B & MIT Alewife made this choice

- protocol flexibility adds both performance and cost

15

• the real question is how much of each??

CS6810

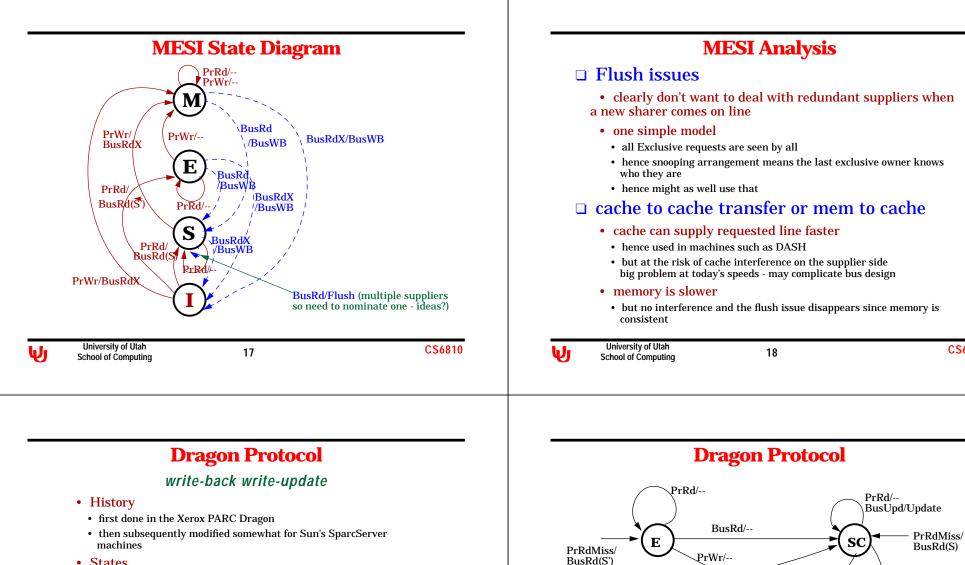

# **MESI Protocol**

# Deals with PrRd followed by PrWr problem

- which generates 2 bus transactions in the MSI protocol

- even when no sharers exist

- adds E (exclusive state)

- intermediate binding between the S and M states

- means exclusive clean e.g. memory is consistent

- M now means exclusive dirty e.g. memory is inconsistent

- S now means 2 or more sharers and memory is consistent

- I is the same

- **S** semantics has an additional implication

- a shared signal must be added to the bus

- single wire is sufficient, implemented via a wired OR

- BusRd(S) indicates the shared signal is asserted on a Bus read

- Bus Rd(S') indicates the shared signal is not asserted on a Bus read

- Bus Rd means we don't care about the shared signal

CS6810

PrWr/

PrRd/--

PrWr/--

BusUpd(S')

PrWrMiss/BusRd(S')

CS6810

PrWr/

BusRd/BusWB

20

PrWr/BusUpd(S')

BusUpd(S)

Μ

BusUpd/Update

SM

PrRd/-

University of Utah

School of Computing

PrWr/BusUpd(S) BusRd/BusWB

PrWrMiss/ BusRd(S);

BusUpd

- States

- · E exclusive clean only one cache has this copy memory OK

- · SC shared clean two or more processors have a copy this one is clean but one of the others may not be hence memory OK isn't known

- SM shared modified 2 or more copies this one must be used to update main memory

- M modified exclusive dirty

- · no I state: although it is implicitly there via an initialization hack and not necessary subsequently since the update protocol doesn't invalidate

- New bus transactions

- BusUpd update bus with the same shared S and S' distinction

19

CS6810

# **Dragon Analysis**

### □ Cache Replacement

- also ignored in the other protocols

- · what needs to be changed

- should others be notified via a bus transaction or not?

- · think about what's in the critical path

- · since we care about overall performance not just a particular transaction

### □ General discussion

- what happens as we go to multilevel caches?

- what happens as we go to split transaction bus designs? · today's norm and imposed by 800MHz + bus clock speeds

- what happens as the compiler reorders instructions?

- what happens as the machine reorders and speculatively executes instructions?

| ህ | University of Utah<br>School of Computing | 21 | CS6810 |

|---|-------------------------------------------|----|--------|

# Note: 2 key issues

# □ Local cache state

- is now extended to include MESI, MSI, etc. + V, D, I status tags

- · hence policy for shared vs. non-shared data may vary

- e.g. write to a shared line effectively writes through

- · write to a private line may follow a write-back policy

- unit of accounting is the cache line

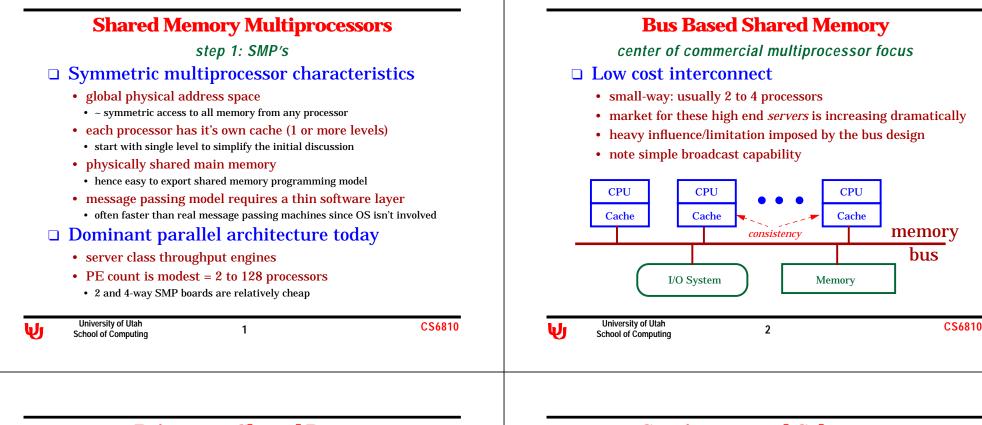

### □ New miss source = coherence miss

- 2 critical subtypes since hit/miss is to a line

- true shared miss ==> miss caused by read and writes to same target

23

• false sharing ==> sharing of line but not the actual datum

# **2 Ported Cache Controller**

#### look at CPU and the bus = problems

### □ Problem source = tag interference

- either transaction requires checking the same tags

- consider the meaning w.r.t. cache organization options

- fully associative, direct mapped, and the hybrid set-associative ??

- □ 2 options both can create stalls

- duplicating tags or ports (which organization applies to each?)

- · when can the snoop completion be delayed

- multilevel cache with *inclusion*

- · higher levels are subsets of lower levels

- lower levels filter interference from L1

- still when L1 copy exists the same snoop delay can occur = stall CPU

22

· of course L2 cache tags could also be duplicated to further reduce contention but this starts to get expensive

University of Utah School of Computing

CS6810

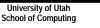

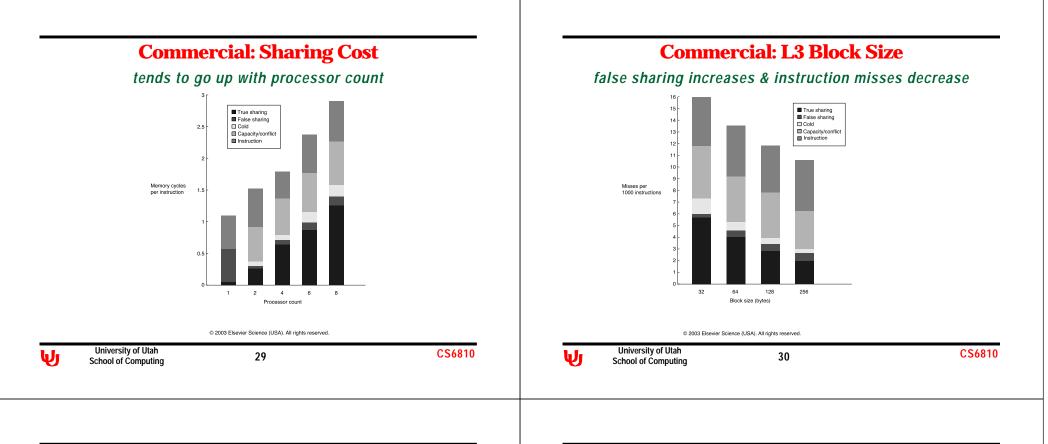

# **Classifying Misses**

#### in a particular reference stream

### □ Idea

- define the *lifetime* for a block in the cache

- do per word accounting

- · this line invalidated due to word FOO reference in another processor

- then distinguish between the various miss types

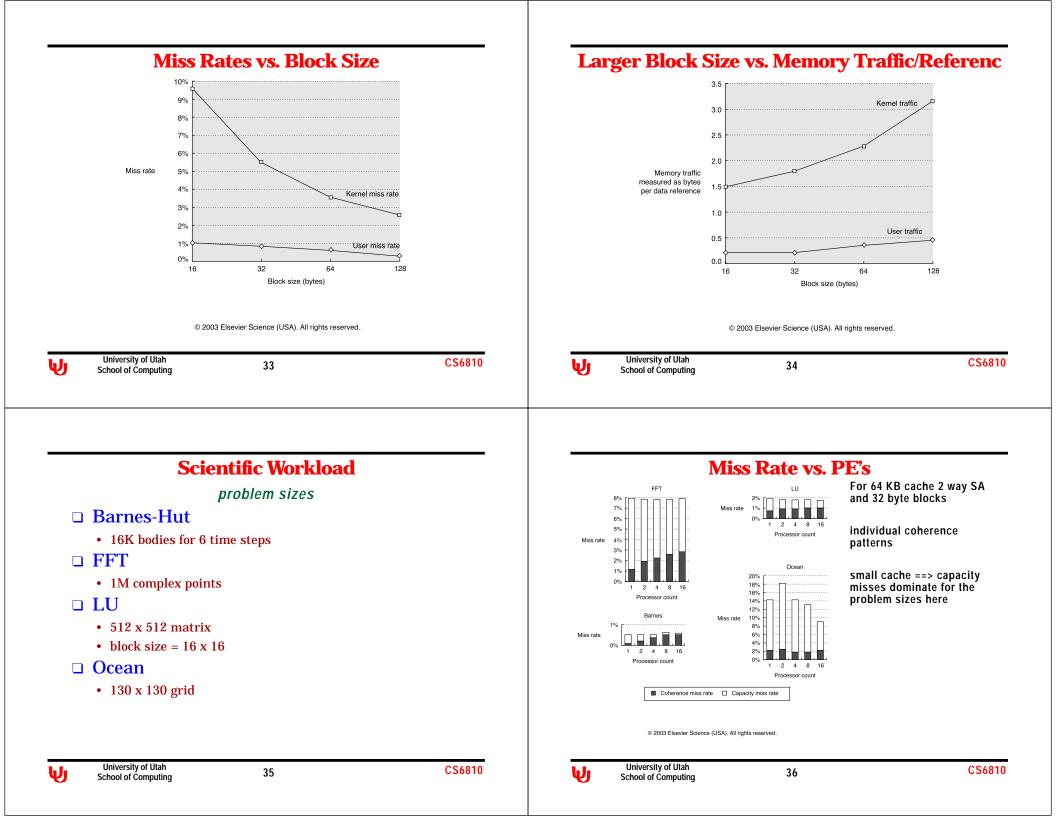

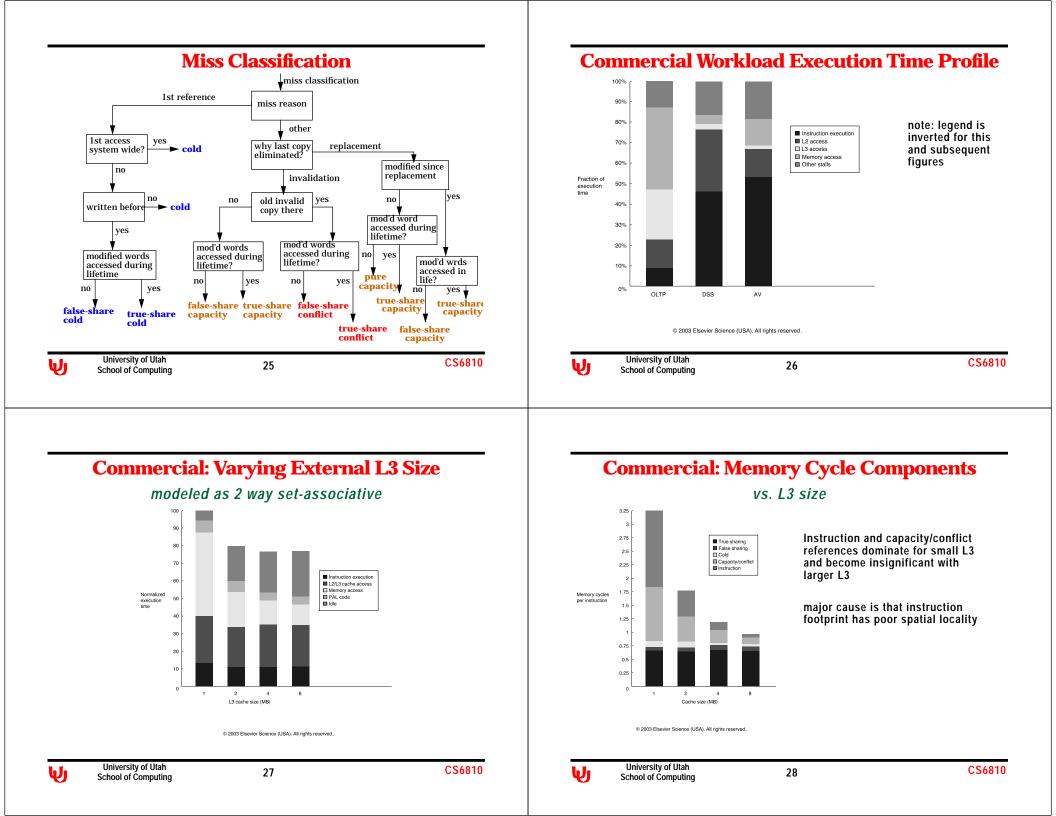

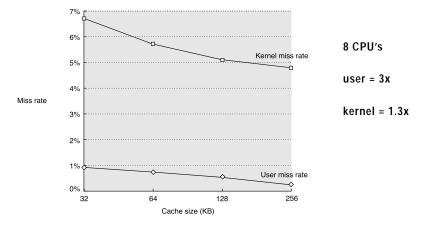

# **Multiprogrammed Workload Performance**

□ Model

- 2 independent makes on 8 processors

- □ 2 components

- kernel vs. user code

- interference increases cold, capacity, and conflict miss rates

# Kernel & User Code Miss Rate vs. Size

#### $\ensuremath{\textcircled{\sc c}}$ 2003 Elsevier Science (USA). All rights reserved.

31

CS6810

32