# REGISTER ALLOCATION USING CIRCULAR FIFOS

Imed Eddine Bennour

El Mostapha Aboulhamid

Département d'Informatique et Recherche Opérationnelle Université de Montréal CP 6128 Centre Ville, Montréal, H3C-3J7, QC, CANADA {aboulham,bennour}@iro.umontreal.ca

#### **ABSTRACT**

In this paper, we study the memory allocation problem in data path synthesis. We propose a register organization called *circular FIFO* as an alternative to register file organization. In comparison with register file organization, FIFO organization eliminates the overhead of address generation and decoding hardware. The memory allocation problem, based on the circular FIFO organization, has been solved efficiently using constraint logic and interval constraint programming.

## 1. INTRODUCTION

A common approach to high level synthesis involves data-flow graph scheduling, functional unit allocation, interconnection and memory allocation. Memory allocation maps constants and variables of a data-flow graph to storage elements (e.g., ROM, registers, register files). Both storage elements and their control part occupy a significant portion of the chip area. Therefore, it is important to minimize the number of storage elements and to organize them in such a way that control, address generation and decoding hardware are reduced. Conventional memory allocation approaches [1-3] can be classified into two categories. In the first category, variables are mapped to registers based on a lifetime analysis of variables. The lifetime interval of a variable is the time interval between its first value assignment and its last use. Multiple variables can share a same register if their lifetime intervals do not overlap with one another. Lifetime analysis approaches aim to minimize the number of registers but not the control hardware. In the second category, variables are mapped to registers which are then grouped into register files (or multiport memories) based on disjoint access time. Register file organization is profitable only if the number and the size of register files are small due to address generation and decoding hardware overhead. Recently, Aloqeely et al. [6] have proposed the use of sequencers as an alternative to register files. Queues and stacks are examples of sequencers. However, their approach has some limitations: first, except queues, sequencers are costly in implementation and, therefore, they cannot be used in a large number; second, the allocation method is suitable only for regular iterative applications where the access patterns of variables are highly regular and uniform, e.g., most variables have the same lifetime duration.

In this paper, we propose: (1) a register organization, called circular FIFO, as an alternative to separated register organization and register file organization, and as an extension of queues [6], (2) the use of the constraint logic programming and the relational interval paradigms to resolve the circular FIFO allocation problem. The circularity in the FIFO adds more flexibility to data access capability: it allows multi-access to a same data, and it removes the

first-in first-out constraint between data, since a data item can be reinjected in the header once it reaches the tail. Separated register organization is a special case of the FIFO organization where each FIFO contains only one register. By grouping registers into FIFOs, we reduce the number of control signals. In the FIFO based architecture register files may still be used, but in a reduced number. To resolve the FIFO allocation problem, we used CLP-BNR [4], a constraint logic programming (CLP) language, based on Prolog augmented with relational interval arithmetic.

The organization of the paper is as follows. Section 2 defines the FIFO allocation problem. Section 3 presents an overview of the interval constraint paradigm, and a formulation of the FIFO allocation problem using interval constraints. Finally, experimental results are presented in section 4.

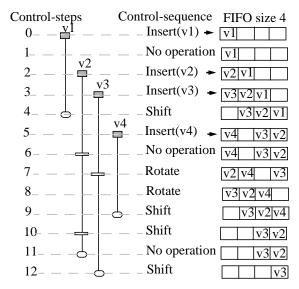

□ : write-time□ : read-time○ : last read-time

Figure 1. Illustration of the functioning of the circular FIFO

## 2. PROBLEM DEFINITION

A circular FIFO is defined by a set of shift registers  $(R_0,R_1,...,R_{M-1})$ , where  $R_i$  is connected to  $R_{i+1}$ , for i=0,...,M-2, and  $R_{M-1}$  is connected to  $R_0$ . The leftmost register  $(R_0)$  and the rightmost register  $(R_{M-1})$  are called *the header* and *the tail of the FIFO*, respectively. Data enter the FIFO from the header and are visible only at the tail. A circular FIFO is controlled by three operations:

- *Insert* ( $v_i$ ): insertion of a variable labelled  $v_i$  in the FIFO header. After an insertion all registers of the FIFO are right shifted and the data item in the FIFO tail is lost.

- Shift: right shift all registers.

- Rotate: it is equivalent to Insert (content of the tail).

During a control-step, at most one control-operation can be performed on the FIFO. A variable  $v_i$  is defined by its write-time and its read-time(s), fixed by the scheduling task.

$$v_i$$

: (Write-time<sub>i</sub>, Read-time<sub>i</sub><sup>1</sup>, Read-time<sub>i</sub><sup>2</sup>, ..., Read-time<sub>i</sub><sup>n<sub>i</sub></sup>)

$v_i$  should be inserted in a FIFO at  $\mathit{Write-time}_i$ , and it should be available in the FIFO tail at each  $\mathit{Read-time}_i^j$ , for  $j=1,...,n_i$ . The lifetime interval of  $v_i$  is equal to  $[\mathit{Write-time}_i, \mathit{Read-time}_i^j]$ .

Figure 1 illustrates the functioning of the circular FIFO. The circularity in the FIFO allows multi-access to a same variable (e.g.,  $v_2$ ), and it removes the first-in first-out constraint (e.g.,  $v_3$  enters the FIFO before  $v_4$  and leaves after  $v_4$ ). A control sequence of a circular FIFO is a sequence of control operations (insert, rotate, shift, no operation). A control sequence is valid for a set of variables, if it guarantees that each variable in the set is inserted in the FIFO at its writing time, and it is available in the tail at its reading time(s). It may happen that, no valid control sequence exists for a set of variables, i.e., variables in this set cannot be mapped into a same FIFO.

Now we can define the two following problems:

- The single-FIFO allocation problem: Given a set of variables  $V = \{v_i\}$ , defined by their write-time and read-time(s), can these variables be mapped to a same circular FIFO? If they can, what is the minimum size of such a FIFO?

- The multi-FIFO allocation problem: Given a set of variables  $V = \{v_i\}$ , defined by their write-time and read-time(s), find a mapping from V to circular FIFOs that optimizes the number of FIFOs and the total number of registers.

We suspect that the single-FIFO allocation problem is NP-complete. We solve it exactly using CLP and interval constraint paradigms. The multi-FIFO allocation problem is NP-hard. A heuristic approach is taken to resolve it. It is based on iterative resolutions of the single-FIFO allocation problem. The following steps summarize this heuristic (developed also using the same CLP environment):

- The set of variables V is divided into disjoint *clusters* (subsets)  $C_l$  such that: (1) variables in the same cluster do not have neither the same writing-times nor the same reading-times, (2) if two variables  $v_i$  and  $v_j$  belong to a same cluster and the writing-time of  $v_i$  is greater than the writing-time of  $v_i$  then the reading-time of  $v_j$  is greater than the reading-time of  $v_i$ , (3) in each cluster  $C_l$ , the maximum number of variables alive at the same time is smaller than or equal to the minimum life-time among all variables in  $C_l$ . These criteria increase the likelihood of mapping successfully all variables in a cluster to a same circular FIFO.

- For each cluster, check if it can be mapped to a same circular FIFO using the exact resolution of the single-FIFO problem. If not, the variables causing the failure are removed from the current cluster and are redistributed on other clusters if possible. New clusters are added if necessary. This process is

repeated until all the clusters are mapped to some feasible circular FIFOs.

- The last step is to reduce the number of clusters, i.e., the number of circular FIFOs. Repetitively, we pick the cluster containing the minimum number of variables, then we try to redistribute all its variables on the other clusters. We check if a variable can be added into a cluster by solving the single-FIFO problem. This process is repeated until all the clusters are considered.

# 3. FORMULATION OF THE SINGLE-FIFO ALLOCATION PROBLEM USING INTERVAL CONSTRAINTS

#### 3.1 A brief overview of the interval constraint paradigm

The use of interval arithmetic [4] [5] allows reasoning about domains of variables rather than fixed values. An interval is a closed bounded set of numbers, it defines either a continuous range of real numbers laying between a lower and an upper bound or a discrete range of integer values laying between integer bounds. The two endpoints of an interval X are denoted by  $\overline{X}$  and X. Thus,  $X = [X, \overline{X}]$ . Two intervals are equal if their corresponding endpoints are *equal*. If x is in the interval X, we write  $x \in X$ . Operations on intervals can be either the basic arithmetic operations defined on the reals  $(+, -, *, /, \min, \max, \sin, \cos, \text{etc.})$ , or arithmetic relations (equality, inequality, inclusion, etc.). In the following, we give a semantic of some of these operations.

• Arithmetic operations:

$$\begin{aligned} & [\underline{X}, \overline{X}] + [\underline{Y}, \overline{Y}] = [\underline{X} + \underline{Y}, \overline{X} + \overline{Y}] \\ & -X = -[\underline{X}, \overline{X}] = [-\overline{X}, -\underline{X}] = \{-x \mid x \in X\} \\ & max(X, Y) = [max(\underline{X}, \underline{Y}), max(\overline{X}, \overline{Y})] \end{aligned}$$

• Arithmetic relations

The *equality constraint* between two intervals X and Y, denoted X == Y, is true if X and Y can be constrained to be equal by *narrowing* (reducing) X and/or Y. For example, if X = [2, 5] and Y = [4, 8], then X == Y is true, since both X and Y can be reduced to the same interval [4, 5]. If X = [2, 5] and Y = [6, 8], then X == Y is false.

The *less than or equal constraint* between an interval X and an interval Y, denoted  $X \le Y$ , is true if the interval X can be constrained to an interval Z where each element of Z is less than or equal to an element of Y. For example, if X = [2, 15] and Y = [6, 8], then  $X \le Y$  is true since X can be reduced to the interval [2, 8] which is less than or equal to Y. If X = [9, 15] and Y = [6, 8], then  $X \le Y$  is false.

## **3.2** Formulation of the single-FIFO allocation problem

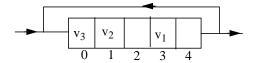

The formulation of the single-FIFO allocation problem is based on the successive states of the FIFO during the execution of a control sequence (sequence of shift, insert and rotate operation). If we label the shift registers composing a circular FIFO from 0 to M-1, then a FIFO state can be defined by the set of variables inside the FIFO and their position. The *distance* from a variable  $v_i$  to a variable  $v_j$ , denote by  $Dist(v_i, v_j)$ , is defined as following:

$Dist(v_i, v_j) = (pos(v_j) - pos(v_i)) \mod M$ where  $pos(v_i)$  is the  $v_i$  position inside the FIFO. Example:

$$Dist(v_2, v_1) = (3-1) \mod 5 = 2$$

$Dist(v_2, v_3) = (0-1) \mod 5 = 4$

Based on the distance definition, we have:

$$\begin{aligned} Dist(v_i, v_j) &\in [0, M-1], \ \forall v_i, v_j \ , \ \text{where } M \text{ is the FIFO size} \\ Dist(v_i, v_i) &= 0, \ \forall v_i \\ Dist(v_i, v_j) &= M - Dist(v_j, v_i), \quad \forall v_i \neq v_j \\ Dist(v_i, v_j) &= (Dist(v_i, v_k) + Dist(v_k, v_j)) modulo \ M, \\ \forall v_i \neq v_i \neq v_k \end{aligned}$$

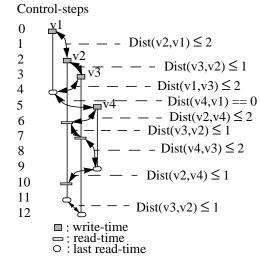

Notice that, due to the last equality, the distance is still defined even between variables which are not into the FIFO at the same time (i.e., variables which are not alive at the same time). Thus, the distance values between pairs of variables are sufficient to capture all the successive states taken by FIFO during the execution of a control sequence. It can be proved that finding a valid control sequence for a set of variables is equivalent to finding feasible distance values among variables. To state the constraints which a distance between two variables should satisfy, we distinguish four cases depending on the precedence order between their write and read operations.

Case 1: two successive write operations

$Dist(v_i, v_i) \leq Write-time_i - Write-time_i$

because between the insertion-time of  $v_i$  and the insertion-time of  $v_j$  into the FIFO the maximum number of control operations (shift, insert, rotate) that can be done is equal to (Write-time  $_i$  – Write-time  $_i$  – 1).

Case 2: two successive read operations  $Dist(v_j, v_i) \leq Read\text{-}time_j^k - Read\text{-}time_i^l$  This constraint guarantees that, after the reading-time of  $v_i$  there are still enough control-steps to propagate  $v_j$  until the FIFO tail.

Case 3: write operation followed by read operation  $Dist(v_j, v_i) \leq Read\text{-}time_j^k - Write\text{-}time_i + 1$  This constraint guarantees that, after the writing-time of  $v_i$  there are still enough control-steps to propagate  $v_j$  until the FIFO tail.

Case 4: read operation followed by write operation

$$Dist(v_j, v_i) = M - 1$$

, if  $Write-time_j = Read-time_i^l$

$Dist(v_j, v_i) \le Write-time_j - Read-time_i^l - 1$ , otherwise

If  $Write-time_j = Read-time_i^l$ , then the constraint states that when  $v_j$  is inserted in the FIFO header  $v_i$  should be in the tail; otherwise it states that between the reading-time of  $v_i$  and the writing-time of  $v_i$  in the FIFO the maximum number of shift

and rotate operations that can be done is equal to  $(Write-time_i - Read-time_i^l - 1)$ .

Figure 2 shows the set of distance constraints for the example used in Figure 1.

Figure 2. Distance constraints for the example used in Figure 1

Now we give the complete formulation of the single-FIFO allocation problem using relational interval arithmetic:

Minimize the FIFO size M under:

(a)  $M \in [M\_min, M\_max]$  where  $M\_min$  is the maximum number of variables alive at the same time, and

$$M_{max} = Min_{v_i} (Read-time_i^1 - Write-time_i + 1)$$

- (b)  $Dist(v_i, v_j) \in [1, M-1], \forall v_i \neq v_j \text{ and } v_i, v_j$  are alive at the same time

- (c)  $Dist(v_i, v_j) \in [0, M-1], \forall v_i \neq v_j \text{ and } v_i, v_j$  are not alive at the same time

- (d)  $Dist(v_i, v_i) = = (M Dist(v_i, v_i))$  ,  $\forall v_i \neq v_i$

- (e)  $Dist(v_i, v_j) == (Dist(v_i, v_k) + Dist(v_k, v_j)) modulo M,$  $\forall v_i \neq v_i \neq v_k$

- (f)  $Dist(v_i, v_i) \le c_f$

Constraint (a) defines the possible values of the FIFO size. Constraint (b) states that variables which are alive at the same time cannot share the same registers into the FIFO: their distances should be greater than zero. Constraints (c), (d) and (e) are the distance's properties. (f) is the set of distance constraints between variables that should be satisfied, as discussed previously in cases (1) to (4).

# 4. IMPLEMENTATION AND EXPERIMENTAL RESULTS

We present in Tables 1 and 2 experimental results obtained using the proposed circular FIFO allocation approach. Table 1 summarizes the results of four benchmarks frequently used by the high level synthesis community. All benchmarks are scheduled using one adder and one multiplier. The second column of Table 1 indicates the minimum number of registers necessary to hold

variables and constants. This number corresponds to the maximum number of variables and constants alive at the same time. The third column corresponds to the number of circular FIFOs obtained using our allocation approach. The total number of registers used in the final design is indicated in the fourth column. We observe that the number of registers used is always optimum, and that these registers are grouped in a small number of FIFOs, which reduces considerably the control signals. To evaluate the efficiency of our approach in general case, we have used random examples, which are more complex than usual high level synthesis benchmarks. The results are given in Table 2. For each example, we generate a set of variables with random lifetime intervals, then we perform the FIFO allocation algorithm. The results are quite interesting. First, the number of circular FIFO (third column) is very small comparatively to the minimum number of registers (second column), in average each FIFO contains five to six registers. Second, the total number of registers used (fourth column) exceeds the optimum by 3 registers at most. We have performed the Aloquely's allocation method [6] on the same random examples, the number of queues returned is on average equal to the number of registers, i.e., most queues contain only one register and hence there is no gain comparatively to the separated register organization. This result is not surprising, since Aloqeely's approach assumes that most variables have the same lifetime durations, which is not the case for the randomly generated examples.

Table1: Benchmark results

| Benchmarks         | Min. # of reg. | # of<br>FIFOs | # of reg.<br>used | CPU (sec.) |

|--------------------|----------------|---------------|-------------------|------------|

| IIR filter         | 20             | 5             | 20                | 10         |

| FIR filter         | 15             | 3             | 15                | 7          |

| Polynomial divider | 15             | 3             | 15                | 7          |

| Three order filter | 7              | 2             | 7                 | 2          |

Table2: Experimental results using random examples

| # of<br>variables | Min. #<br>of reg. | # of<br>FIFOs | # of reg.<br>used | CPU time (sec.) |

|-------------------|-------------------|---------------|-------------------|-----------------|

| 30                | 16                | 3             | 18                | 44              |

| 30                | 18                | 4             | 18                | 32              |

| 30                | 17                | 3             | 17                | 494             |

| 30                | 20                | 4             | 21                | 63              |

| 50                | 26                | 4             | 27                | 85              |

| 50                | 23                | 5             | 26                | 86              |

| 50                | 28                | 4             | 30                | 66              |

| 50                | 22                | 4             | 25                | 76              |

Table2: Experimental results using random examples

| # of<br>variables | Min. #<br>of reg. | # of<br>FIFOs | # of reg.<br>used | CPU time (sec.) |

|-------------------|-------------------|---------------|-------------------|-----------------|

| 70                | 37                | 5             | 39                | 155             |

| 70                | 30                | 5             | 32                | 82              |

| 70                | 33                | 6             | 36                | 109             |

| 70                | 34                | 6             | 36                | 52              |

| 100               | 50                | 7             | 53                | 158             |

| 100               | 42                | 6             | 45                | 221             |

| 100               | 43                | 6             | 45                | 239             |

| 100               | 39                | 5             | 42                | 198             |

#### 5. CONCLUSIONS

We presented a new regular register organization, circular FIFO, as an alternative to separated register organization and to register file organization. Grouping registers into circular FIFOs reduces the control hardware without increasing the number of storage elements. In comparison with register file organization, FIFO organization eliminates the overhead of address generation, decoding hardware and the extra access delay. The efficiency of the approach was tested on benchmarks and on complex random examples. Using a complex practical problem like the FIFO allocation problem, we found that the constraint logic programming based on relational interval constraint is a very promising paradigm for solving other CAD problems.

#### REFERENCES

- [1] G. De Micheli, *Synthesis and Optimization of Digital Circuits*, McGraw-Hill, New York, 1994.

- [2] D. Gajski, N. Dutt, A. Wu, and S. Lin, *High-Level Synthesis*, Kluwer Academic Publishers, Boston, 1992.

- [3] R. Walker and R. Camposano, *A Survey of High-Level Synthesis Systems*, Kluwer Academic Publishers, Boston, 1991.

- [4] BNR PROLOG, User Guide, Version 4, 1993.

- [5] R.E. Moore, *Methods and Applications of Interval Analysis*, SIAM, 1979.

- [6] M. Aloqeely and C. Y. Roger Chen, "Sequencer-Based Data Path Synthesis of Regular Iterative Algorithms", In Proc. of the 31 st Design Automation Conference, 1994.