#### Université de Montréal

## Covérification des Systèmes Intégrés

par

#### Mostafa Azizi

Département d'Informatique et de Recherche Opérationnelle Faculté des Arts et des Sciences

Thèse présentée à la Faculté des Études Supérieures en vue de l'obtention du grade de Philosophiæ Doctor (Ph. D.) en Informatique

Décembre 2000

@Azizi Mostafa, 2000

### Université de Montréal

Faculté des Études Supérieures

Cette thèse intitulée:

## Covérification des Systèmes Intégrés

présentée par :

#### Mostafa Azizi

a été évaluée par un jury composé des personnes suivantes :

| Mme Rachida Dssouli       | Président – Rapporteur   |

|---------------------------|--------------------------|

| M. El Mostapha Aboulhamid | Directeur de recherche   |

| M. Sofiène Tahar          | Codirecteur de recherche |

| M. Guy Bois               | Membre du jury           |

| M. Claude Thibault        | Examinateur externe      |

| M                         | Représentant du doyen    |

|                           |                          |

| Thèse acceptée le :       |                          |

## **Sommaire**

u cours des décennies passées, la conception des composantes logicielle et matérielle d'un système intégré s'effectuait séparément. Puis, le logiciel (abrégé par L) obtenu était exécuté sur le matériel (abrégé par M) prototype. Si les contraintes de la spécification requises pour le système ne sont pas satisfaites, le processus de conception est réitéré dans l'espoir de retrouver un bon prototype. Cette technique de vérification des propriétés d'un tel système s'est avérée lourdement coûteuse en termes du temps de réalisation et du coût du système global. Pour remédier ... une telle situation, plusieurs compagnies et universités se sont penchées sur l'élaboration d'environnements de codesign L/M ayant de meilleures performances. Aussi, ces derniers devront-ils intégrer des outils efficaces et fiables pour accomplir des tâches de covérification. Afin d'atteindre un niveau maximum de succès, la covérification doit être exécutée en concurrence avec le codesign; en d'autres mots, il est nécessaire qu'elle soit intégrée au codesign dès ses premières phases.

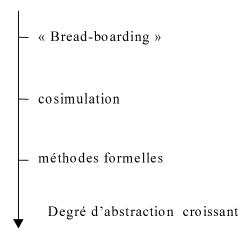

La covérification, a priori, peut être effectuée par trois techniques principales : « bread-boarding », cosimulation et covérification formelle. La première est utilisée rarement ou lorsque les autres méthodes échouent. La troisième technique, elle et la vérification formelle se chevauchent largement et elle nécessite d'être revue et développée. Quant " la deuxième, la cosimulation, elle est abondamment utilisée pour les systèmes mixtes " tel point qu'on confond les termes covérification et cosimulation; elle consiste " simuler simultanément les parties logicielle et matérielle d'un système tout en assurant la communication entre les deux. Nous proposons dans cette thèse d'améliorer cette technique par une méthodologie combinant les concepts de base de la simulation, des inspirations de la vérification formelle et des techniques de la programmation orientée objet.

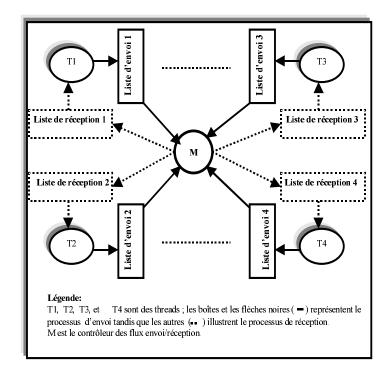

Notre méthodologie de covérification est basée sur le concept du «multithreading». Dans cette approche, la partie logicielle est décrite par un ensemble de threads communicants, l'interaction entre les deux parties logicielle et matérielle s'effectue via des registres, et des threads additionnels sont utilisés pour exprimer des assertions de vérification. Finalement, la cosimulation du code global est exécuté comme un modèle unifié (homogène) à l'aide du compilateur Java ou comme un modèle distribué (hétérogène) à l'aide d'un environnement de covérification.

Partant d'une spécification d'un système L/M, le concepteur travaille à parfaire sa conception et à coder correctement son implémentation. Mais comme personne n'est parfaite, il y a toujours une probabilité de présence d'erreurs au moins implicites (de fonctionnalité) dans le code (des centaines de lignes) bien que sa compilation soit accomplie avec succès (c'est-à-dire sa syntaxe est correcte). Cette situation de doute exige une validation de l'implémentation par rapport à sa spécification. Pour ce faire, des propriétés extraites de la spécification doivent être satisfaites par l'implémentation globale des deux parties logicielle et matérielle, y compris leur interface de communication.

Les propriétés décrivent un tout ou une partie de la spécification du système L/M. Leurs expressions sont formulées en combinant éventuellement des paramètres de la partie logicielle seule, de la partie hardware seule ou des deux à la fois. Ces propriétés sont définies selon les formats d'écriture d'une propriété en CPL («Coverification Properties Language»). CPL est un langage simple que nous avons développé afin de décrire, séparément de l'implémentation, l'ensemble des propriétés à covérifier par notre outil JACOV («JAva COVerification tool»). Ces propriétés contenues dans un fichier sont ensuite traduites et rangées dans des threads de Java.

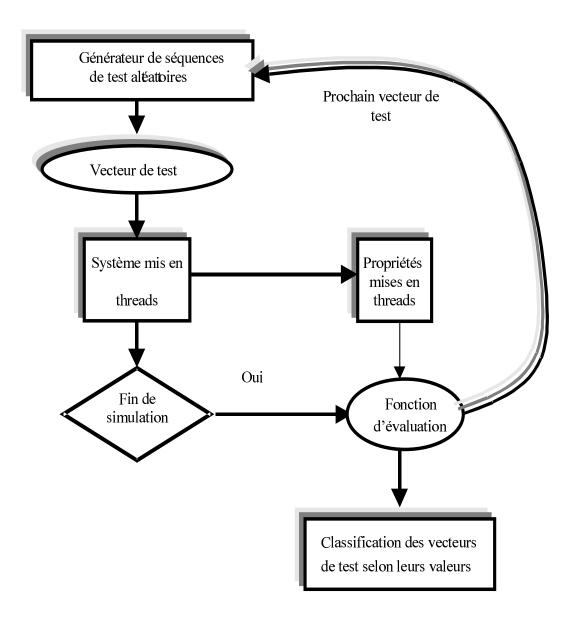

La covérification des propriétés susmentionnées est effectuée par un processus de simulation/cosimulation. Étant donné que le système et ses propriétés à covérifier sont répartis en threads, nous amorçons la simulation par une séquence significative de vecteurs de test. Cette séquence devrait être choisie de manière à ce que les propriétés réagissent à l'application de chacun de ses éléments (de la séquence). Les réponses de toutes les propriétés recueillies durant la simulation sont analysées pour conclure des chances de réussite de la covérification. Si une des propriétés a fait preuve d'un comportement incorrect, alors ceci est un signe suffisant de la présence d'une anomalie au sein de l'implémentation (sachant bien sûr que toutes les propriétés sont correctes des points de vue de la syntaxe et de la logique). Toutefois, si toutes les propriétés ont satisfait les tests qu'elles ont subis, alors la covérification est prometteuse mais elle ne garantit pas que l'implémentation soit absolument correcte.

Avant de conclure cette thèse, nous avons appliqué notre méthodologie sur un modèle d'un système à plusieurs processeurs et à mémoire partagée afin de contrôler la cohérence des données des différentes caches (chaque processeur en possède une). Nous avons observé et illustré les traces du flux de données du système dans les deux cas : sans et avec protocole de cohérence; les résultats obtenus sont très positifs. Nous avons fait aussi une vérification formelle du même système par la technique de «model checking» offerte par l'outil VIS («Verification Interacting with Synthesis tool») et montré l'aspect de complémentarité entre la covérification et la vérification formelle surtout quand la réalisation de cette dernière s'avère très coûteuse ou impossible.

# Mots clés

Covérification L/M

Vérification formelle

Cosimulation

Threads

Propriétés

Systèmes intégrés

Systèmes L/M

Simulation séquentielle

Simulation distribuée

Spécification

Test

# Table des matières

| SOMMAIRE                                                   | IV        |

|------------------------------------------------------------|-----------|

| MOTS CLÉS                                                  | VI        |

| LISTE DES TABLEAUX                                         | XI        |

| LISTE DES FIGURES                                          | XII       |

| LISTE DES SIGLES ET ABRÉVIATIONS                           | XV        |

| LISTE DES CONTRIBUTIONS                                    | XVI       |

| REMERCIEMENTS                                              | XX        |

| CHAPITRE 1                                                 | 22        |

| INTRODUCTION ET MOTIVATIONS                                | 22        |

| Cadre de la thèse                                          | 24        |

| CONTRIBUTIONS                                              |           |

| PLAN DE LA THÈSE                                           |           |

| CHAPITRE 2                                                 | 28        |

| MÉTHODES DE CONCEPTION ET DE VÉRIFICATION DES CIRCUITS IN  | TÉGRÉS 28 |

| 2.1. Introduction                                          | 28        |

| 2.2. Processus de conception                               |           |

| 2.3. LANGAGES DE DESCRIPTION HDL ET MODÉLISATION           |           |

| 2.3.1. Niveaux d'abstraction                               |           |

| 2.3.2. Langages standards de description de matériel (HDL) |           |

| A. Verilog                                                 |           |

| B. VHDL                                                    |           |

| 2.4. SYNTHÈSE                                              |           |

| 2.5. 1. Modélisation des fautes                            |           |

| 2.5.2. Techniques de simulation des fautes                 |           |

| 2.5.3. Génération automatique des patrons de test          |           |

| 2.5.4. Test fonctionnel                                    |           |

| 2.5.5. Conception prévoyant la testabilité (DFT)           |           |

| 2.6. VÉRIFICATION FORMELLE DU MATÉRIEL                     |           |

| 2.6.1. « Model-Checking »                                  |           |

| 2.6.2. « Theorem-Proving »                                 |           |

| 2.7 CONCLUSION                                             | 44        |

| CHAPITRE 3                                                            | 45 |

|-----------------------------------------------------------------------|----|

| INTRODUCTION AU CODESIGN ET À LA COVÉRIFICATION DES                   |    |

| INTÉGRÉS                                                              |    |

| 3.1. Introduction                                                     |    |

| 3.2. MOTIVATION ET POSITION DU PROBLÈME                               |    |

| 3.2.1. Terminologie                                                   | 46 |

| 3.2.2. Position du problème                                           | 47 |

| 3.3. Codesign L/M                                                     |    |

| 3.4. APERÇU SUR LES TECHNIQUES DE COVÉRIFICATION                      |    |

| 3.4.1. Techniques de représentation                                   | 53 |

| 3.4.2. Mécanismes de la covérification                                | 53 |

| A. Covérification par cosimulation                                    |    |

| B. Covérification par «bread-boarding»                                |    |

| C. Covérification formelle                                            |    |

| 3.4.3. Types d'erreurs                                                |    |

| 3.4.4. Propriétés à vérifier                                          |    |

| 3.4.5. Applicabilité des méthodes de vérification à la covérification |    |

| 3.5. COSIMULATION: TECHNIQUES ET TECHNOLOGIE                          |    |

| 3.5.1. Définition                                                     |    |

| 3.5.2. Techniques de cosimulation                                     |    |

| 3.5.3. Technologie de la cosimulation L/M                             | 59 |

| 3.6. QUELQUES ENVIRONNEMENTS DE CODESIGN ET DE COVÉRIFICATION         | 62 |

| 3.6.1. POLIS                                                          |    |

| 3.6.2. Ptolemy                                                        |    |

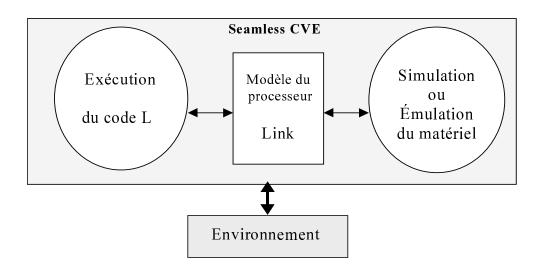

| 3.6.3. CVE-Seamless                                                   |    |

| 3.6.4. Eaglei                                                         |    |

| 3.7. COVÉRIFICATION ORDONNANCÉE                                       |    |

| 3.7.1. Cas sans temporisation                                         |    |

| 3.7.2. Cas avec temporisation                                         |    |

| 3.8. CONCLUSION                                                       | 67 |

|                                                                       |    |

| CHAPITRE 4                                                            | 69 |

|                                                                       |    |

| MÉTHODOLOGIE DE COVÉRIFICATION BASÉE SUR LE « MUTLITHREAI             |    |

| 4.1. Introduction                                                     |    |

| 4.2. TECHNIQUE DE COVÉRIFICATION BASÉE SUR LE « MULTITHREADING »      | 70 |

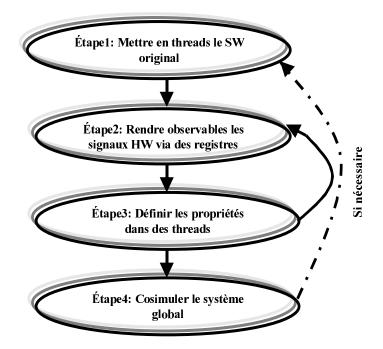

| 4.2.1. Première étape : Mise en threads de la partie logicielle       |    |

| 4.2.2. Deuxième étape : Registres de surveillance                     |    |

| 4.2.3. Troisième étape : Spécification des propriétés                 | 76 |

| 4.2.4. Quatrième étape : Cosimulation du système                      |    |

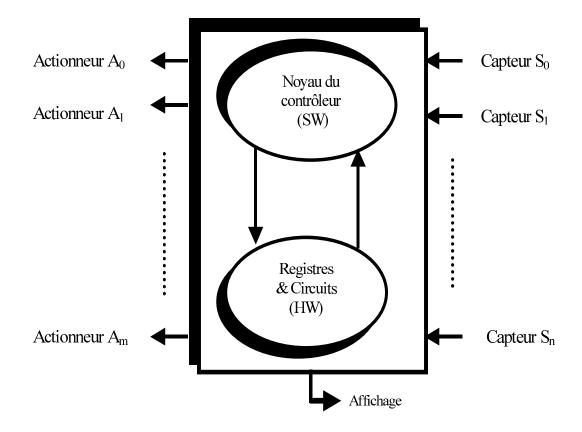

| 4.3. Exemple d'illustration : un contrôleur à logique floue           |    |

| 4.4. IMPLÉMENTATION ET RÉSULTATS                                      |    |

| 4.4.1. Spécification des propriétés                                   | 79 |

| 4.5.2. Structure du code                                              |    |

| 4.5.3. Simulation et test                                             | 83 |

| 4.6. CONCLUSION                                                       | 87 |

| CHAPITRE 5                                                               | 88    |

|--------------------------------------------------------------------------|-------|

| SIMULATIONS SÉQUENTIELLE ET DISTRIBUÉE BASÉES SUR DES THREADS            | 88    |

| 5.1. Introduction                                                        | 88    |

| 5.2. SIMULATION SÉQUENTIELLE (SS)                                        | 90    |

| 5.2.1. Notation                                                          | 90    |

| 5.2.2. Algorithme SS                                                     |       |

| 5.2.3. Exemple d'une ligne d'assemblage                                  | 92    |

| 5.3. SIMULATION DISTRIBUÉE (DS)                                          |       |

| 5.3.1. Algorithme DS                                                     |       |

| 5.3.2. Exemple d'application                                             |       |

| 5.4. VALIDITÉ DES ALGORITHMES SS ET DS                                   |       |

| 5.5. IMPLÉMENTATION                                                      |       |

| 5.5.1. Structure                                                         |       |

| 5.5.2. Gestion des horloges                                              |       |

| 5.5.3. Exemple d'exécution                                               |       |

| 5.6. DISCUSSION                                                          |       |

| 5.6.1. SS ou DS?                                                         |       |

| 5.6.2. Difficultés                                                       |       |

| 5.7. CONCLUSION                                                          | . 107 |

| CHAPITRE 6                                                               | . 108 |

| JACOV : SPÉCIFICATION ET COVÉRIFICATION DES PROPRIÉTÉS                   | . 108 |

| 6.1. Introduction                                                        | . 108 |

| 6.2. Motivations                                                         |       |

| 6.3. CPL: Langage de spécification des propriétés à covérifier par JACOV |       |

| 6.3.1. Définitions                                                       |       |

| 6.3.2. Syntaxe de CPL                                                    |       |

| 6.3.3. Sémantique de CPL                                                 |       |

| 6.3.4. À propos de CPL                                                   |       |

| 6.4. DESCRIPTION ET COVÉRIFICATION DES PROPRIÉTÉS L/M AVEC JACOV         |       |

| 6.4.1. Spécification des propriétés en CPL                               |       |

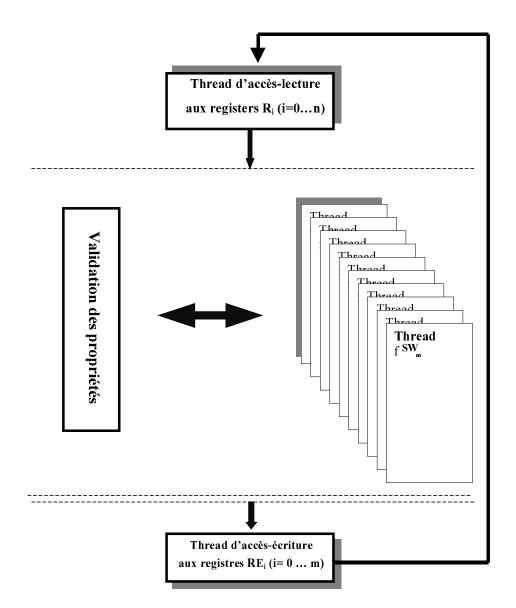

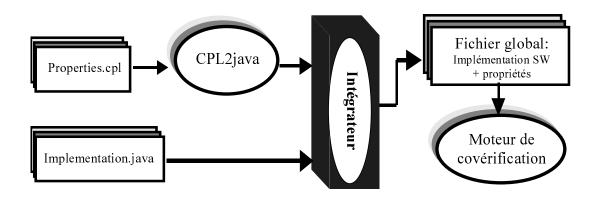

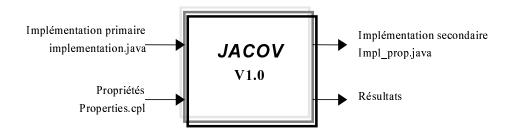

| 6.4.2. Covérification des propriétés avec JACOV                          | . 114 |

| 6.4.3. À propos de JACOV                                                 |       |

| 6.4.4. Activation des propriétés.                                        |       |

| 6.5. CONCLUSION                                                          |       |

| CHAPITRE 7                                                               | . 122 |

| VÉRIFICATION ET COVÉRIFICATION D'UN PROTOCOLE DE COHÉRENCE               |       |

| CACHESCACHES                                                             |       |

| 7.1. Introduction                                                        | . 122 |

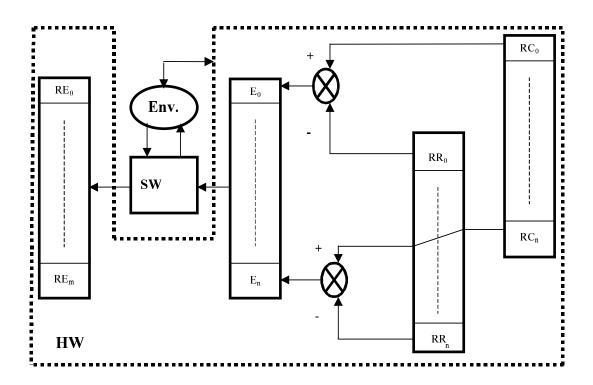

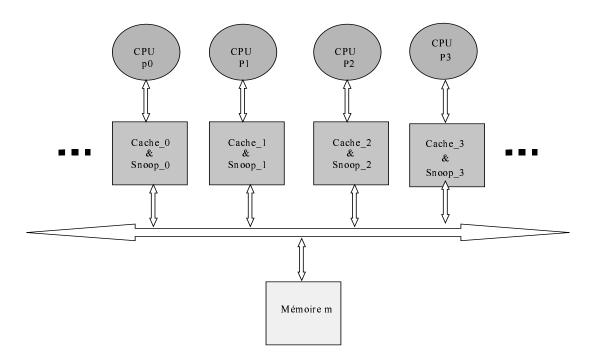

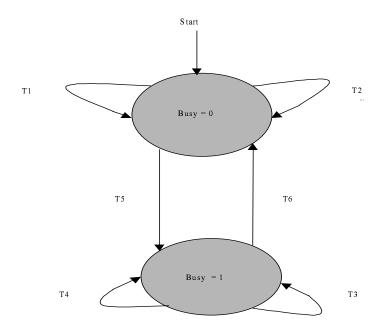

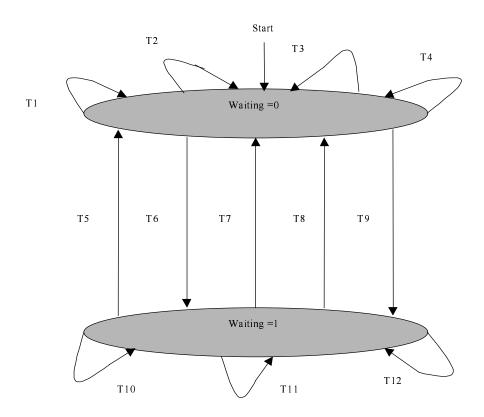

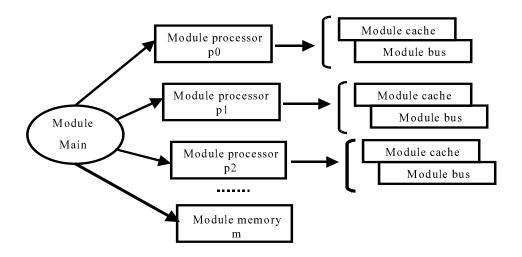

| 7.2. Architecture du système                                             | . 124 |

| 7.3. MODÉLISATION DU SYSTÈME                                             |       |

| 7.3.1. La mémoire partagée                                               |       |

| 7.3.2. Bus partagé                                                       |       |

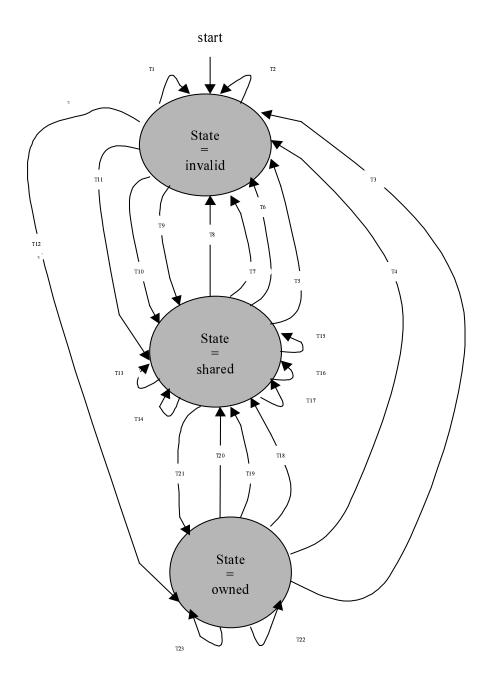

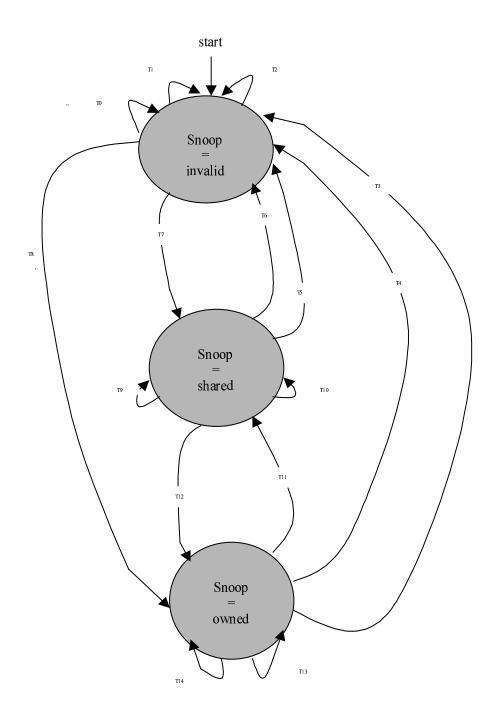

| 7.3.3. Mémoire cache                                                     |       |

| 7.3.4. Processeur                                                        |       |

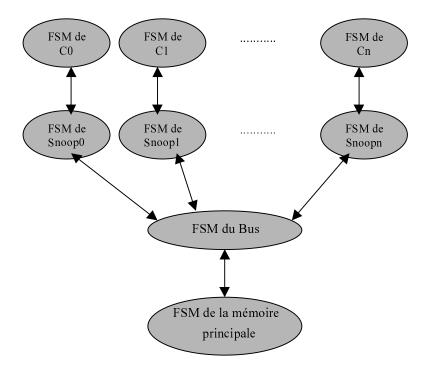

| 7.3.5. FSM du système global                                             |       |

| 7.4. VÉRIFICATION DES PROPRIÉTÉS PAR «MODEL CHECKING»               | 34  |

|---------------------------------------------------------------------|-----|

| 7.4.1. Protocole de cohérence des caches 1                          | 34  |

| 7.4.2. Bus                                                          |     |

| 7.4.3. Mémoire partagée 1                                           |     |

| 7.4.4. Des propriétés de vivacité 1                                 |     |

| 7.5. COVÉRIFICATION DES PROPRIÉTÉS PAR SIMULATION                   | 36  |

| 7.6. IMPLÉMENTATION ET RÉSULTATS                                    |     |

| 7.6.1. Cas de la vérification formelle 1                            | 39  |

| 7.6.2. Cas de la covérification 1                                   |     |

| 7.7. CONCLUSION                                                     |     |

| CHAPITRE 8 1                                                        | .48 |

| CONCLUSION ET PERSPECTIVES 1                                        | 48  |

| Conclusion                                                          | 48  |

| UTILITÉ DE CETTE THÈSE 1                                            | 50  |

| Travaux futurs                                                      | 51  |

| ANNEXE 1 : UN APERÇU SUR LE CODE DE L'ANALYSEUR SYNTAXIQUE DE CPL 1 | 53  |

|                                                                     |     |

| ANNEXE 2 : EXEMPLE SIMPLE DE SIMULATION À L'AIDE DES THREADS 1      | 74  |

|                                                                     |     |

| RÉFÉRENCES 1                                                        | 77  |

| BIBLIOGRAPHIE1                                                      | 85  |

# Liste des tableaux

| Tableau 3.1 : Les différents types de VSP                                         | 62  |

|-----------------------------------------------------------------------------------|-----|

| Tableau 5.1 : Étapes d'exécution de l'exemple 5.2.3 en appliquant l'algorithme SS |     |

| Tableau 5.2 : Étapes d'exécution de l'exemple 5.2.3 en appliquant l'algorithme DS |     |

| Tableau 7.1 : Version CTL des propriétés                                          | 138 |

| Tableau 7.2 : Résultats de la vérification des propriétés                         |     |

| Tableau 7.3 : Simulation du fonctionnement du système                             | 14  |

# Liste des figures

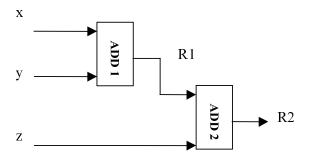

| Figure 2.1 : Additionneur logique                                                 | 33    |

|-----------------------------------------------------------------------------------|-------|

| Figure 2.2 : Structure générale d'un programme en Verilog                         | 33    |

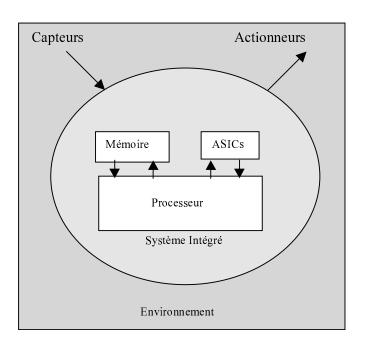

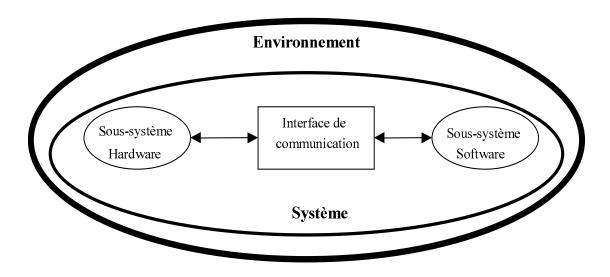

| Figure 3.1 : Un système intégré                                                   | 46    |

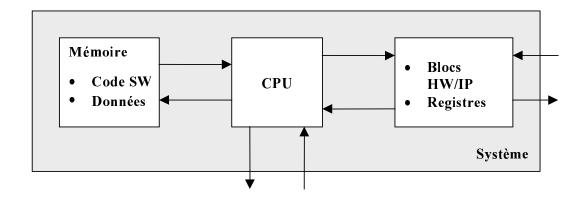

| Figure 3.2 : Représentation globale d'un système intégré                          | 48    |

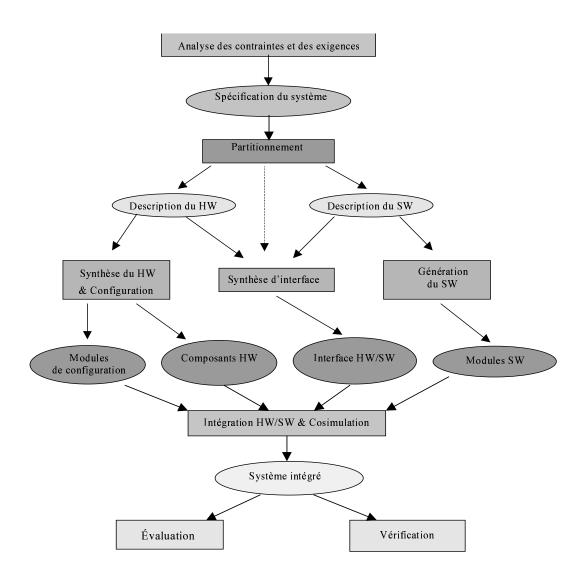

| Figure 3.3 : Flux conventionnel du codesign                                       |       |

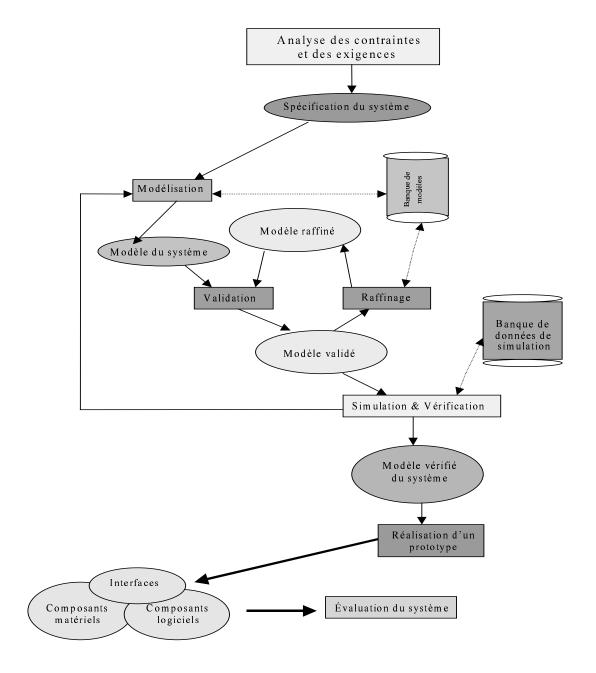

| Figure 3.4 : Flux de codesign basé sur un modèle                                  |       |

| Figure 3.5 : Niveaux d'abstraction des trois méthodologies de covérification      |       |

| Figure 3.6 : Technique de covérification par cosimulation                         |       |

| Figure 3.7 : Technique de covérification par « Bread-boarding »                   |       |

| Figure 3.8 : Technique de covérification formelle                                 |       |

| Figure 3.9 : Vue simplifiée d'Eaglei                                              |       |

| Figure 3.10 : Circuit combinatoire                                                |       |

| Figure 3.11 : Ordonnancement sans horloge                                         |       |

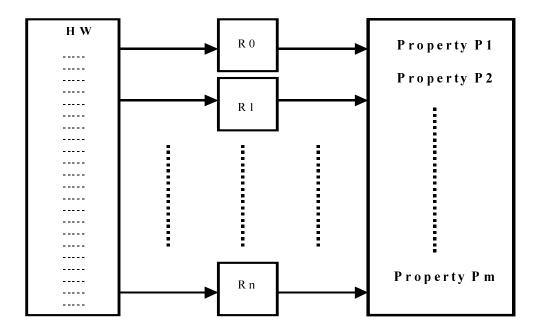

| Figure 4.1 : Architecture comportementale d'un système L/M                        |       |

| Figure 4.2 : Architecture structurelle d'un système L/M                           |       |

| Figure 4.3 : Organisation des codes HLL et HDL                                    |       |

| Figure 4.4 : Registres auxiliaires pour des fins de covérification                |       |

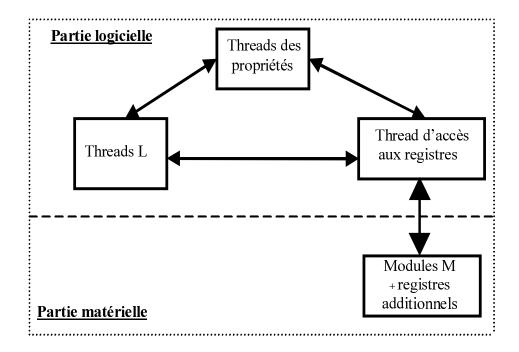

| Figure 4.5 : Logiciel original augmenté par quelques threads                      |       |

| Figure 4.6 : Vue comportementale de cosimulation                                  |       |

| Figure 4.7 : Contrôleur à logique floue                                           |       |

| Figure 4.8 : Description de la partie matérielle                                  | 81    |

| Figure 4.9 : Vue globale de la partie logicielle étendue                          |       |

| Figure 4.10 : Validation des propriétés vs des vecteurs de test                   |       |

| Figure 5.1 : Ligne d'assemblage                                                   |       |

| Figure 5.2 : Vue globale de l'implémentation                                      | . 100 |

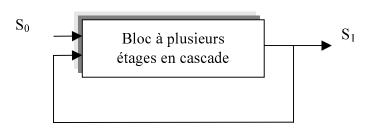

| Figure 5.3 : Un circuit à «feed-back»                                             |       |

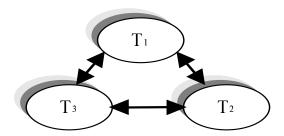

| Figure 5.4 : Exemple de trois threads en communication                            |       |

| Figure 5.5 : Code (a) et Exécution (b) d'un exemple de la simulation séquentielle |       |

| Figure 5.6 : Code (a) et Exécution (b) d'un exemple de la simulation distribuée   |       |

| Figure 6.1 : Flux d'exécution de notre technique de covérification                |       |

| Figure 6.2 : Exemple de propriétés décrites en CPL                                |       |

| Figure 6.3 : Vue globale de l'outil semi-automatique de covérification JACOV      |       |

| Figure 6.4 : Entrées-Sorties de JACOV                                             |       |

| Figure 6.5 : Cas de test aléatoire des propriétés                                 |       |

| Figure 6.6 : Cas de test guidé par des propriétés                                 |       |

| Figure 7.1 : Architecture du système étudié                                       |       |

| Figure 7.2 : FSM de la mémoire partagée                                           |       |

| Figure 7.3 : Module de la mémoire partagée en Verilog                             |       |

| Figure 7.4 : FSM du bus                                                           |       |

| Figure 7.5 : Module du bus en Verilog                                             |       |

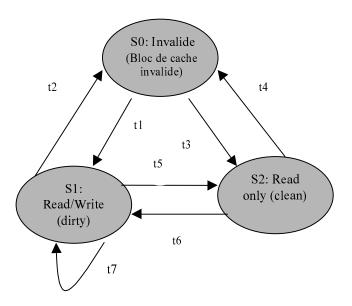

| Figure 7.6: FSM d'un bloc de la cache                                             |       |

| Figure 7.7 : FSM du protocole « snoopy »                                          |       |

| Figure 7.8 : Module de la cache en Verilog                                        |       |

| Figure 7.9 : Module du processeur en Verilog                                      |       |

| Figure 7.10 : Vue globale du code du système                                      |       |

| Figure 7.11 : FSM du système global                                               |       |

| Figure 7.12 : Module principal en Verilog                                         |       |

| Figure 7.13 : Protocole de cohérence des caches                                   |       |

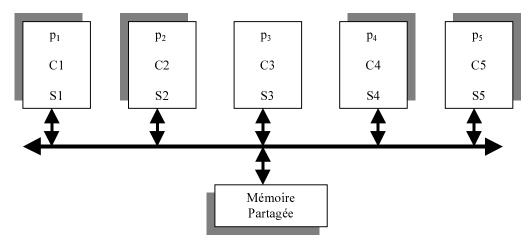

| Figure 7 14 · Système multiprocesseur à mémoire partagée                          | 137   |

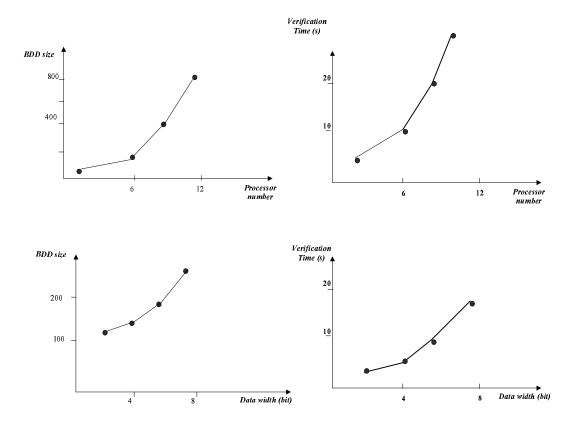

| Figure | 7.15: | Effets de la longueur des données et du nombre de processeurs sur la taille des BDDs | et  |

|--------|-------|--------------------------------------------------------------------------------------|-----|

| le     | temps | s de vérification                                                                    | 140 |

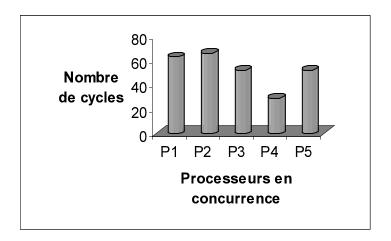

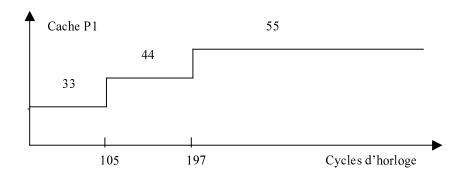

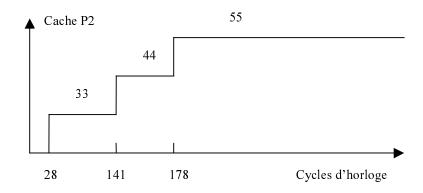

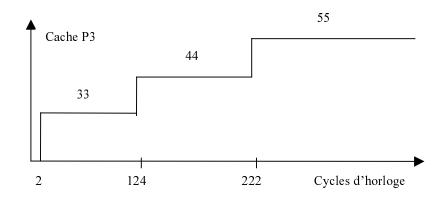

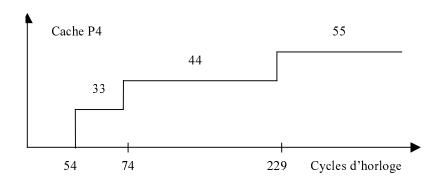

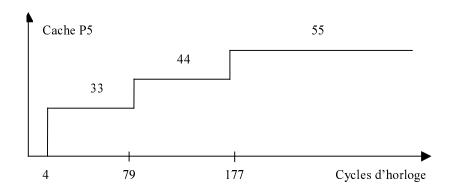

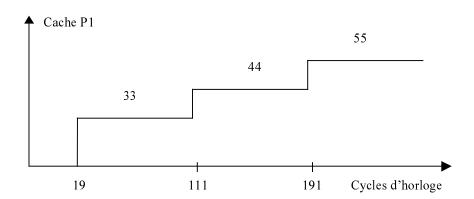

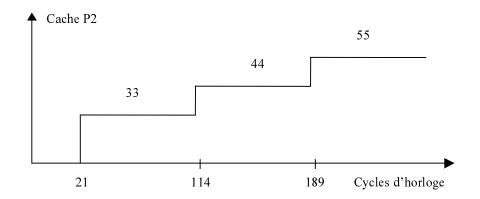

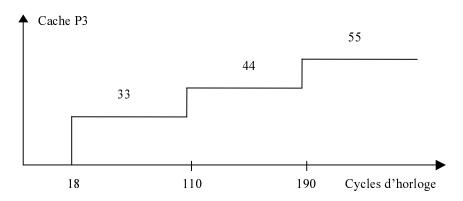

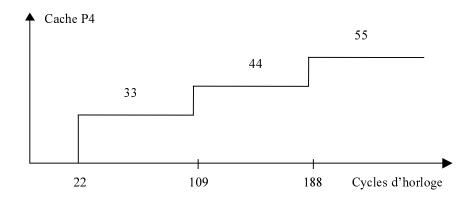

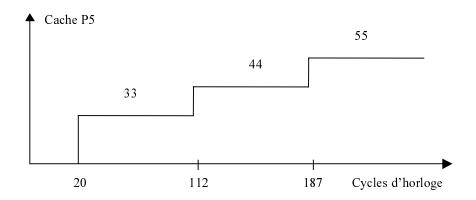

| Figure | 7.16: | Nombre de cycles consommés par chaque processeur                                     | 141 |

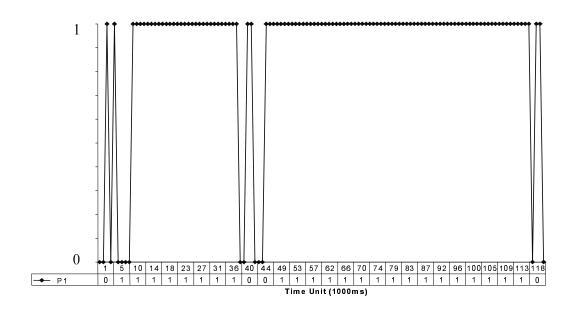

| Figure | 7.17: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>1</sub>  | 142 |

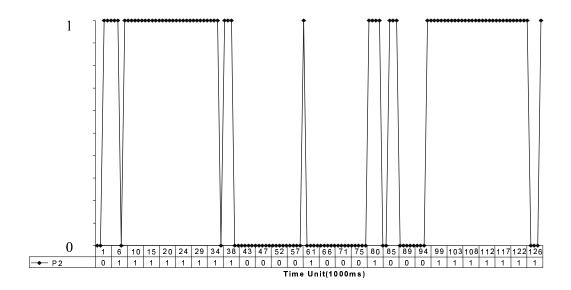

| Figure | 7.18: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>2</sub>  | 142 |

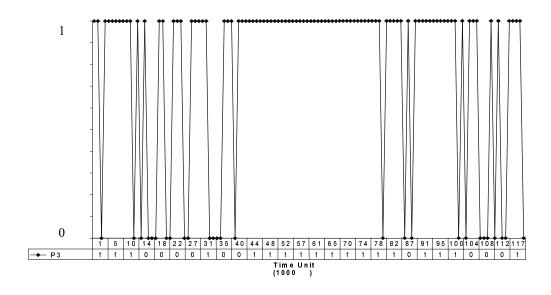

| Figure | 7.19: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>3</sub>  | 143 |

| Figure | 7.20: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>4</sub>  | 143 |

| Figure | 7.21: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>5</sub>  | 143 |

| Figure | 7.22: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>1</sub>  | 144 |

| Figure | 7.23: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>2</sub>  | 145 |

| Figure | 7.24: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>3</sub>  | 145 |

| Figure | 7.25: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>4</sub>  | 145 |

| Figure | 7.26: | Répercussion de la réécriture de la mémoire partagée sur la cache de p <sub>5</sub>  | 146 |

# Liste des sigles et abréviations

AMC Applied Microsystems Corporation

ASIC Application Specific Integrated Circuit

BDD Binary Decision Diagrams

CDFG Control Data Flow Graphs

CFSM Codesign Finite State Machine

CPL Coverification Properties Language

CPU Central Processing Unit

CTL Computation Tree Logic

DS Distributed Simulation

EDA Eagle Design Automation

EFSM Extended Finite State Machine

FIFO First Input First Output

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

HLL High Level Language

HOL High Order Logic

HW Hardware

ICE In-Circuit Emulator

ILA Iterative Logic Array

IP Intellectual Property

ISS Instruction-set Simulator

JACOV JAva-COVerification tool

L Logiciel

LTS Labeled Transition Space

M Matériel

NORTEL NORthern TELecom, Canada

RAM Random Access Memory

RFV Register For Verification

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RTL Register Transfer Level

SS Sequential Simulation

SW Software

VHDL VHSIC Hardware Description Language

VIS Verification Interacting with Synthesis tool

VIS-Verilog Sous-ensemble de Verilog admissible par VIS

VSP Virtual Software Processor

# Liste des contributions<sup>1</sup>

- 1. M. Azizi, E. -M. Aboulhamid, and S. Tahar, "Sequential and Distributed Simulations using Java Threads", Proceedings of the International Conference on Parallel Computing in Electrical Engineering (PARELEC'2000), IEEE Computer Society, pp. 237-241, Trois-Rivières, Quebec, Canada, August 27-30, 2000 (ISBN 0-7695-0759-X)

- **2.** E. -M. Aboulhamid, M. Azizi, and X. Song, "Hardware Design and Verification Methods", Book chapter in the Encyclopedia of Computer Science and Technology, Vol. 42, pp. 67-91, A. Kent and J. G. Williams Eds., Marcel Dekker, Inc., New York, USA, 2000 (ISBN 0-8247-2295-7)

- **3.** M. Azizi, E. -M. Aboulhamid et S. Tahar, "Entre la covérification concurrente et l'ordonnancement des threads", Colloque de la Microélectronique, Congrès ACFAS'2000, Université de Montréal, Montréal, Canada, 10-14 mai 2000 (http://www.acfas.ca/)

- **4.** M. Azizi, E. -M. Aboulhamid, and S. Tahar, "Properties Coverification in HW/SW Systems", Proceedings of the 2<sup>nd</sup> International Conference of Electronic Circuits and Systems (ECS'99), pp. 80-83, Bratislava, Slovakia, September 6-8, 1999 (http://www.ieee.org)

- **5.** M. Azizi, E. -M. Aboulhamid, and S. Tahar, "Multithreading-Based Coverification Technique of HW/SW Systems", Proceedings of the International Conference of Parallel and Distributed Processing Techniques and Applications (PDPTA'99), CSREA Press, Vol. IV, pp. 1999-2005, Las Vegas (Nevada), USA, June 27-30, 1999 (ISBN 1-892512-14-9)

- **6.** M. Azizi, E. -M. Aboulhamid et S. Tahar, "Covérification des systèmes HW/SW basée sur le concept de «multithreading»", Communication au congrès ACFAS'99, Université d'Ottawa, Ottawa, Canada, 10-14 mai 1999 (http://www.acfas.ca/)

- 7. M. Azizi, O. Ait-Mohamed, and X. Song, "Cache Coherence Protocol Verification of a Multiprocessor System with Shared Memory", Proceedings of the 10<sup>th</sup> International Conference of Microelectronics (ICM'98), pp. 99-102, Mounastir, Tunisia, December 17-19, 1998 (http://www.ieee.org)

-

<sup>&</sup>lt;sup>1</sup> Cette liste couvre presque toutes nos contributions durant la période de notre inscription au doctorat (allant de septembre 1996 à décembre 2000).

- **8.** M. Azizi, E. -M. Aboulhamid, and S. Tahar, "Multi-threading Based Coverification of Embedded Systems", Workshop on Block Based Design (BBD'98), Ottawa, Canada, October 1998 (http://www.cmc.ca/)

- **9.** M. Azizi, "Cosimulation using Eaglei Environment", Internal Report, NORTEL Corkstown, Nepean, Canada, March 1998 (5T53/4: team of Cosimulation & Emulation)

- 10. M. Azizi et E. -M. Aboulhamid et I. Bennour, "Covérification des systèmes intégrés : Étude et Analyse", Communication au congrès ACFAS'98, Université Laval, Québec, Canada, mai 1998 (http://www.acfas.ca)

- 11. M. Azizi, E. -M. Aboulhamid et I. Bennour, "Covérification des systèmes intégrés", Actes du Colloque International du Traitement d'Image et des Systèmes de Vision Artificielle (TISVA'98), pp. 234-240, Oujda, Maroc, avril 1998

- **12.** M. Azizi, Covérification des systèmes intégrés, Thèse de doctorat, ∼180 pages, Université de Montréal, Montréal, Canada (dépôt en décembre 2000)

À la mémoire de mes chers parents bba Abd Allah et mma Rahma!

À toute ma famille!

À tous les bons de ce monde!

...

## Remerciements

Nous tenons à exprimer notre reconnaissance envers :

- monsieur El Mostapha Aboulhamid, professeur agréé à l'Université de Montréal et notre directeur de recherche,

- monsieur Sofiène Tahar, «associate professor» à la «Concordia University» et notre codirecteur de recherche,

- tous deux pour leur soutien continu, leurs conseils avisés et la patience dont ils ont dû faire preuve à notre égard.

- madame Rachida Dssouli (Université de Montréal), monsieur Guy Bois (École Polytechnique de Montréal), monsieur Claude Thibault (École de Technologie Supérieure de Montréal) et tous les autres membres du jury pour avoir accepté d'examiner cette thèse.

- l'ACDI, le GRIAO, le Ministère de l'Enseignement Supérieur du Maroc et la FES de l'Université de Montréal pour leur soutien financier.

- monsieur Parviz Youssefpur, manager à NORTEL, pour nous avoir offert un stage au sein des groupes : «5T53 : Methodologies of Design Systems» et «5T54 : Cosimulation & Emulation» à «NORTEL Semi-conductors» (Ottawa), pour la période allant de novembre 97 à mars 98.

- messieurs Shailish Saturwala et Imed Bennour, respectivement senior et junior à NORTEL, pour nous avoir supervisé durant notre séjour à NORTEL.

- tous nos enseignants depuis la maternelle.

- nos sœurs et frères pour leur encouragement permanent.

- ma femme pour sa compréhension et son soutien continu.

- nos collègues au DIRO (Université de Montréal) et à l'École Supérieure de Technologie d'Oujda (Maroc).

# Chapitre 1

## Introduction et Motivations

epuis quelques années, de nombreuses prédictions sur le futur de l'ordinateur font la une des médias de l'informatique. Ces prédictions, en fait, reposent sur des tentatives récentes de mise au point de nouveaux ordinateurs en faisant appel à des technologies substitutives de la micro-électronique de manière complète ou au moins partielle. Alors, nous entendons de nos jours parler de l'ordinateur optique basé sur la photonique, de l'ordinateur moléculaire basé sur la chimie des molécules, de l'ordinateur biologique basé sur l'exploitation des neurones vivants, de l'ordinateur à base d'ADN et de l'ordinateur quantique basé sur la physique quantique de la matière [8]. Ces différents genres d'ordinateurs sont tous en phase de recherche et leur émergence éventuelle sur le marché public serait tributaire du dilemme performance/coût et d'une compétitivité convaincante avec l'ordinateur micro-électronique. En attendant ce que ramènent les vagues du futur pour savoir davantage sur la relève de la micro-électronique, cette dernière n'a pas encore dit son dernier mot et semble capable de persévérer bien longtemps.

La micro-électronique connaît actuellement une révolution sans pareille sur tous les plans, industriels et académiques. Ceci a donné naissance à des systèmes très complexes aussi bien au niveau de leurs conceptions qu'au niveau de leurs fonctionnements. Pour veiller sur la crédibilité de leurs conceptions, ces systèmes doivent être soumis à des processus de vérification et de test assez rigoureux. Une telle tâche n'est point évidente vu l'accroissement rapide de la complexité et de l'hétérogénéité des « nouveau-nés » micro-électroniques.

En fonction de leurs spécifications et des performances désirées, différentes architectures sont considérées pour réaliser ces systèmes. Notre intérêt de recherche est concentré sur les systèmes dits mixtes<sup>2</sup> ou intégrés. Il s'agit de systèmes à deux dimensions, une logicielle et une autre matérielle. De tels systèmes trouvent leur application dans plusieurs domaines tels que la Télécommunication, l'Aéronautique, la Robotique, l'Automobile, la Médecine, etc.

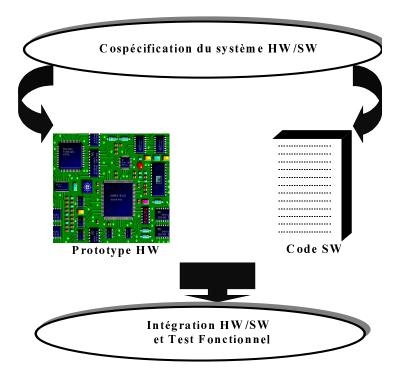

La conception des composantes logicielle et matérielle d'un système intégré, au cours des décennies passées, s'effectuait de manière séparée. Puis, la partie logicielle obtenue était exécutée sur le prototype de la partie matérielle. Si les contraintes de la spécification requises pour le système ne sont pas satisfaites par le design, le processus est réitéré dans l'espoir de retrouver un bon prototype. Cette technique de vérification des propriétés d'un tel système s'est avérée lourdement coûteuse en termes de temps de réalisation et de coût du système global. Pour remédier à une telle situation, plusieurs compagnies et universités ont axé leurs intérêts sur l'élaboration d'environnements de codesign de meilleures performances. Aussi, ces derniers devront-ils intégrer des outils efficaces et fiables pour accomplir des tâches de covérification. Dans l'objectif d'atteindre un niveau maximum de succès, la covérification doit être exécutée en concurrence avec le codesign; en d'autres mots, il est nécessaire qu'elle soit intégrée au codesign dès ses premières phases.

<sup>&</sup>lt;sup>2</sup> Nous entendons par système mixte, un système à deux parties logicielle et matérielle. Il ne faut pas faire la confusion avec un système à deux parties analogique et numérique.

La covérification d'un système intégré, étant une nouvelle perception de la vérification de ses deux parties constituantes au fur et à mesure que le design se réalise, revêt un intérêt potentiel dans le monde des circuits intégrés dédiés à des applications spécifiques (ASIC) ou générales (GPIC). L'utilisation de ces derniers est très abondante, mais la maîtrise de leur complexité n'est guère à la portée des concepteurs puisqu'elle se complique davantage à chaque jour. Ce qui explique la demande pressante d'outils puissants pour la conception, la vérification et la réalisation de tels systèmes. Comme remède, de nombreuses tentatives académiques et industrielles ont fait l'objet de plusieurs articles sans réussir toutefois à satisfaire les exigences de qualité et d'efficacité. De notre côté, nous tentons d'apporter une modeste contribution dans ce domaine en proposant un nombre de techniques d'amélioration de la covérification.

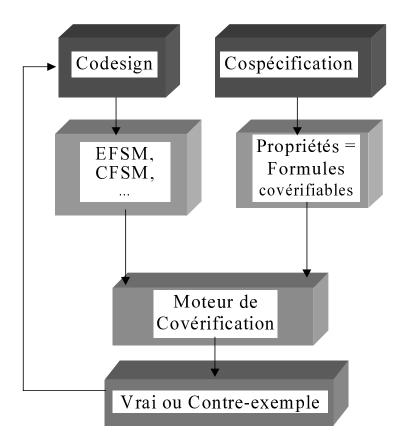

A priori, la covérification peut être effectuée par trois techniques principales : « bread-boarding » (c'est-à-dire vérifier après le prototypage), cosimulation et covérification formelle. La première n'est utilisée que peu ou lorsque les autres méthodes échouent (dans le cas d'un système matériel, on parle de « testing »). La troisième technique, la covérification formelle, se chevauche largement avec la vérification formelle et elle nécessite d'être revue et développée. Quant à la deuxième, la cosimulation, elle est souvent utilisée pour les systèmes mixtes à tel point qu'on confond les termes covérification et cosimulation. Elle consiste à simuler simultanément les parties du système, logicielle et matérielle, tout en assurant la communication entre les deux. Nous proposons d'améliorer cette technique par une méthodologie combinant les concepts de base de la simulation, des inspirations de la vérification formelle et des techniques de la programmation orientée objet.

#### Cadre de la thèse

Cette thèse met l'emphase sur une nouvelle piste de recherche : la covérification des systèmes L/M. La littérature est très riche de travaux sur la vérification des systèmes micro-électroniques à caractère matériel (ASICs, VLSI,...).

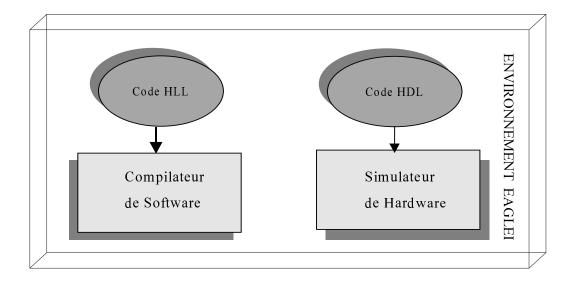

Toutefois, à cause de certaines raisons de partitionnement lors de la conception d'un système donné, des fonctions spécifiques sont réalisées par un programme (microcode) et non par un circuit (câblage). Un tel processus de conception est connu sous le nom de « HW/SW-codesign ». Dans cette situation, le système en cours de conception est mixte; il a deux parties : une logicielle et une autre matérielle. Qu'allons nous faire pour vérifier un tel genre de systèmes? Faut-il appliquer les techniques de vérification du matériel en faisant abstraction de la partie logicielle ou vice versa? Ou avant tout, est-ce que les techniques antérieures de vérification formelle sont applicables même sur un système mixte en cours de conception? La majorité des techniques de vérification formelle font souvent appel à la théorie des automates (ou équivalents), qui sert comme une piste de décollage vers une abstraction souvent très floue d'un point de vue pratique. Le concepteur soucieux des devenirs concrets des signaux internes ou externes du système, opte généralement pour une simulation ou un test afin de traquer explicitement les flux de contrôle et de données du système. En outre, dans le cas des systèmes L/M, il n'y a pratiquement aucune méthode (ou outil) formelle pour une telle vérification. Cela est dû à la difficulté de « matérialiser » la partie logicielle afin de profiter des outils et des techniques disponibles de la vérification matérielle. En attendant que le comportement logiciel soit efficacement reproduit par des composants matériels, l'intérêt est maintenant concentré sur la covérification par cosimulation. Notre thèse s'inscrit alors dans ce cadre. Elle dévoile les secrets de cet axe de recherche tout en y effectuant les contributions listées ci-après.

## Contributions<sup>4</sup>

Nos principales contributions sont résumées par les points suivants :

i. Identification de la covérification : nous avons classifié les techniques de cosimulation existantes en littérature récente tout en présentant les outils qui leur

<sup>&</sup>lt;sup>3</sup> C'est-à-dire donner un comportement matériel à la partie logicielle pour en fin de compte manipuler le système mixte (hétérogène) comme un système matériel (homogène).

<sup>&</sup>lt;sup>4</sup> Voir la liste des contributions, page xviii.

sont associés. En plus, nous avons donné plus de sens au terme « covérification » en expliquant ses objectifs, ses techniques et ses domaines d'application.

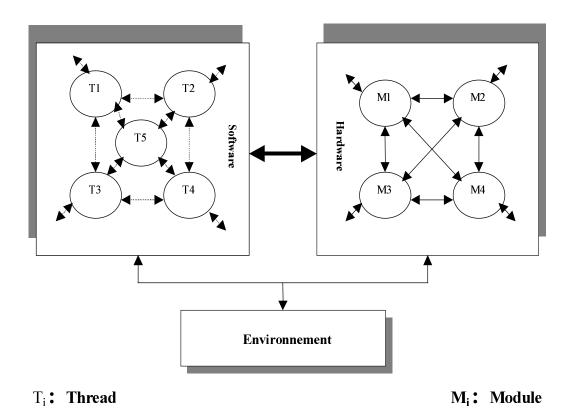

ii. Méthodologie de covérification basée sur le «multithreading» : nous avons proposé une méthodologie basée sur le concept du «multithreading» pour effectuer une covérification des systèmes L/M. Elle évalue par cosimulation les propriétés du système étudié. Cette méthodologie se prête aussi bien aux systèmes mixtes (à deux dimensions logicielle et matérielle) qu'aux systèmes non mixtes (à une seule dimension, soit logicielle soit matérielle).

iii. Spécification des propriétés : les propriétés à covérifier sont décrites dans un langage simple que nous avons développé spécialement pour cette fin. Ce langage portant le nom CPL («Coverification Properties Language»), permet à son utilisateur de spécifier les propriétés du système dans une syntaxe similaire à celles des langages de haut niveau (Java par exemple). Les propriétés décrites en CPL devront être automatiquement converties en threads et intégrées au design du système, sans toutefois le modifier.

- iv. Cosimulations séquentielle et distribuée : sous une optique de covérification, nous avons réécrit et implémenté avec succès les algorithmes classiques des simulations, séquentielle et distribuée, en utilisant les threads. Les résultats obtenus sont très prometteurs.

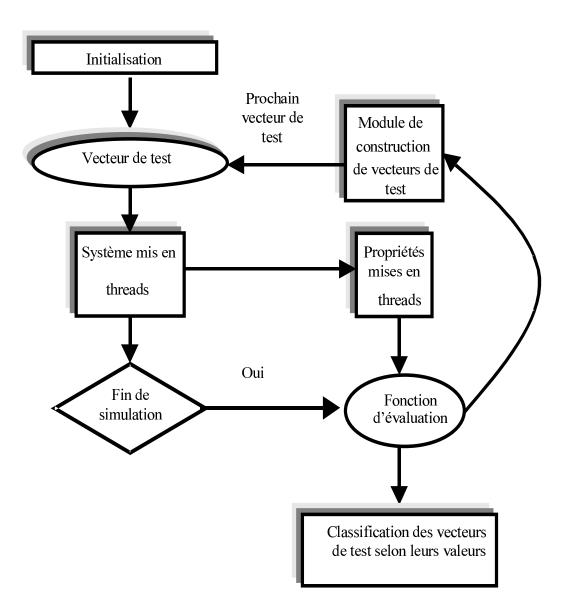

- v. Tests orientés par des propriétés : nous avons tenté de classifier les vecteurs de test à la lumière de leurs activations des propriétés considérées. Un vecteur de test est qualifié de « bon » si son application à l'entrée du système fait activer un bon nombre de propriétés. Dans une première simulation, une séquence aléatoire de vecteurs de test est appliquée au système. Pour chaque vecteur, nous générons un rapport sur l'activation des propriétés. Seuls les bons vecteurs de la séquence courante seront considérés pour les futures simulations. Les bons vecteurs sont soumis à des fonctions de transformation déterministes, aléatoires ou mixtes dans

l'espoir d'améliorer la qualité des vecteurs de test générés. Une fonction d'évaluation s'occupe de la tâche de sélection des bons vecteurs de test.

#### Plan de la thèse

Notre thèse est organisée de la manière suivante. Le chapitre 1 présente une introduction générale au sujet de cette thèse tout en discutant ses motivations et sa problématique. Le chapitre 2 rapporte les travaux publiés dans les domaines de la conception et de la vérification du matériel. Ce chapitre permet au lecteur de situer le thème de la covérification par rapport à ces axes de recherche, et de comprendre nos propos dans les chapitres suivants. Nous résumons dans le chapitre 3 les principaux techniques et outils contemporains de la cosimulation tout en faisant la liaison avec le codesign et la covérification des systèmes L/M. En plus, nous discutons dans ce chapitre l'ordonnancement des threads en Java et comment ces derniers pourront être utilisés pour faire de la covérification concurrente. Au chapitre 4, nous proposons une méthodologie de covérification basée sur le principe du «multithreading». Cette méthodologie est considérée comme un apport innovateur dans cet axe de recherche. Basée sur des threads, une réimplantation des algorithmes classiques des simulations séquentielle et distribuée est discutée au sein du chapitre 5. Le chapitre 6 explique comment spécifier les propriétés à covérifier selon notre méthodologie. Nous avons défini pour cette fin une syntaxe baptisée CPL. Le chapitre 7 expose deux applications, l'une de vérification et l'autre de covérification. Par-là, nous visons à démontrer le rôle complémentaire de la covérification par rapport à la vérification formelle. Le dernier chapitre conclut notre thèse et suggère des axes de recherche futurs pour donner suite à notre travail.

# Chapitre 2

# Méthodes de conception et de vérification des circuits intégrés

#### 2.1. Introduction

Les systèmes et les composants micro-électroniques sont de plus en plus intégrés dans différents systèmes dédiés ou au sein d'applications importantes telles que les télécommunications, l'avionique, l'automatique, la robotique, l'appareillage électronique, etc. Certains de ces systèmes micro-électroniques sont très complexes; ils peuvent être perçus comme étant une interconnexion de blocs contenant chacun des millions de transistors. Souvent, lorsque les concepteurs sont en train de concevoir un matériel pour une application spécifique, ils choisissent des composants préconçus, déjà testés et essayés. La réutilisation du design devient de plus en plus populaire puisqu'elle permet de réduire aussi bien le temps de réalisation d'un circuit que son coût. Les tâches de test et de vérification débutent maintenant au niveau comportemental où l'intégration des composants est une importante solution. Le concepteur dispose d'une spécification complète ou partielle du système global ou du composant spécifique qui doit être conçu à partir d'ingrédients micro-électroniques

disponibles. La spécification est réalisée à l'aide du paradigme des langages de description de matériel (HDL); elle peut être exécutée, simulée ou éventuellement soumise à des outils d'évaluation, d'estimation ou de vérification. La spécification est alors supposée être sans fautes et elle peut être utilisée comme un modèle de référence pour vérifier la conformité de toute implémentation par rapport à la spécification originale. Dû à la complexité ascendante des systèmes micro-électroniques récents, de nouveaux axes de recherche ont vu le jour pour combler les lacunes des anciennes techniques. Nous citons à titre d'exemple le codesign L/M, la réutilisation du design (« design reuse ») et la vérification formelle.

Afin de situer la covérification par rapport aux autres tâches de conception et rendre ainsi nos propos compréhensibles pour un lecteur non averti, ce chapitre donne un aperçu sur les techniques de conception et de vérification. La section 2.2 traite les différentes étapes du processus de conception. Une vue succincte sur les langages HDL fait l'objet de la section 2.3. Dans la section 2.4, nous exposons très brièvement l'objectif de la synthèse des systèmes numériques. La vérification basée sur la simulation ou le test, est présentée dans la section 2.5; nous y discutons aussi les techniques de simulation, de conception testable et de génération automatique de test, ainsi que les modèles de fautes. La vérification formelle du matériel est rapportée dans la section 2.6. La section 2.7 conclut ce chapitre.

## 2.2. Processus de conception

Le processus de conception est un ensemble d'actions, ordonnées et bien définies, à exécuter par l'outil ou l'opérateur de conception pour satisfaire une spécification d'un système, des consignes ou des objectifs prédéfinis. Ces actions sont étroitement dépendantes de la nature du système en cours de conception. D'où, il n'y a pas une méthode unique pour concevoir des systèmes différents, cependant la philosophie y demeure globalement la même. Le processus de conception accueille à son entrée la spécification d'un produit et génère à sa sortie l'implémentation de celui-ci. Fournie par le client, la spécification englobe toutes ou quelques consignes que l'implémentation du produit doive satisfaire. L'implémentation peut être

élaborée à n'importe quel niveau d'abstraction dépendamment de là où les paramètres des propriétés de la spécification seront bien explicites et le test d'équivalence de l'implémentation avec la spécification pourrait être accompli sans aucun problème.

Les processus de conception sont classifiés en deux grandes catégories :

- La conception personnalisée (« *custom design* ») : elle est coûteuse et requiert des efforts colossaux, alors son utilisation est limitée à des applications spécifiques telles que la conception des unités de processeurs.

- La conception semi-personnalisée (« semi-custom design ») : elle représente avec la méthodologie de la conception réutilisable une bonne alternative de la conception personnalisée. La conception semi-personnalisée peut être répartie en deux types : le design à base de cellules et le design à base de tableaux. Le premier s'effectue en utilisant des cellules de la librairie (des cellules); quant au second, il utilise des modules MPGAs et FPGAs [9].

Généralement, le processus de conception comprend les étapes suivantes :

- *Modélisation*: Partant d'une spécification dans un langage naturel ou d'une description écrite dans un langage de spécification, un modèle HDL du système est établi. Un tel modèle doit être validé avant de procéder à l'étape suivante. Par ailleurs, les langages VHDL et Verilog sont actuellement les plus populaires des langages de description du matériel.

- *Synthèse*: Le modèle HDL obtenu est optimisé à la lumière de certaines contraintes telles que le temps d'exécution, la surface du circuit et son coût. Pour ce faire, des outils de synthèse permettant de faire l'optimisation nécessaire et de générer le schéma du circuit, sont largement utilisés (Synopsys, Cadence, etc.).

- *Validation*: Cette étape finale vérifie si le modèle implémenté reproduit exactement la fonctionnalité du modèle spécifié (modèle de référence). Après l'étape de validation, viennent les phases de mise en prototype et de fabrication.

#### 2.3. Langages de description HDL et modélisation

Un modèle reproduit, selon ses raisons d'être, certaines caractéristiques du système original. Il peut être élaboré à n'importe quel niveau d'abstraction et sous un format textuel (code), graphique (graphe) ou mixte.

#### 2.3.1. Niveaux d'abstraction

L'abstraction est un concept basé sur le fait d'ignorer ou de supprimer dans un modèle certains détails du système original afin de simplifier sa taille (du modèle), d'en déduire des conclusions d'ordre général et aussi pour réduire le volume du travail requis. On distingue plusieurs niveaux d'abstraction :

- *Niveau système*: on essaye à ce niveau d'identifier l'architecture globale du système en spécifiant ses principaux éléments et leurs communications bilatérales et avec l'environnement. À ce niveau, on ne s'intéresse pas aux détails des composants du système, une vue globale suffit.

- *Niveau comportemental* : la fonctionnalité d'un composant matériel à ce niveau est décrite depuis ses ports d'entrée jusqu'à ses ports de sortie. Le « timing » n'est pas requis dans le modèle; cependant, il peut y être considéré afin de servir de repère pour certaines exécutions.

- *Niveau transfert de registres (RTL)*: à ce niveau, on suppose que le système est synchrone. Des contraintes sur le «timing» et les ressources du système sont définies. Le comportement de chaque composant est donc décrit pour chaque cycle d'horloge. Les opérations des flux de contrôle et de données sont accomplies à l'aide des registres.

- *Niveau porte* : le système à ce niveau est globalement vu comme étant un circuit séquentiel. Ce dernier pourrait comprendre des bascules, des loquets et des portes logiques. Un tel modèle peut être dérivé d'une description RTL tout en faisant usage des librairies des différentes technologies (TTL, CMOS, etc.). Ces dernières, créées sous une optique de réutilisation, regroupent des modèles « clé en main » de bascules et de portes.

- *Niveau transistor et mise en carte* : à ce niveau, le système paraît comme étant une carte portant plusieurs composants actifs (transistors) et passifs (résistances, capacités, etc.). Une optimisation des emplacements des composants sur la surface offerte s'en suit.

#### 2.3.2. Langages standards de description de matériel (HDL)

L'objectif de ces langages est de faciliter les tâches de modélisation des composants numériques et d'en élaborer une documentation exécutable. La maintenance du code HDL et l'insertion de nouveaux composants au sein d'un design existant, sont devenues relativement faciles et requièrent sensiblement moins de temps. Les HDLs sont indépendants de la technologie, cependant ils permettent d'adapter un même modèle à différentes technologies. Les HDLs les plus fréquemment utilisés sont Verilog et VHDL.

#### A. Verilog

Verilog [10, 11] est un langage de description de matériel dédié en premier lieu à la modélisation et à la simulation des circuits logiques avec un degré d'efficacité satisfaisant. Il est conçu à base du langage C. En comparaison avec VHDL, Verilog est un langage faiblement typé. Il permet d'implémenter des exécutions séquentielles et parallèles. Un composant en Verilog est décrit par l'objet *module* (figure 2.1) dont il faut déclarer les entrées-sorties et spécifier la fonction. Nous illustrons ci-après sur la figure 2.2 une structure typique d'un programme Verilog.

Un module peut aussi faire appel aux services d'autres modules en les instantiant dans son corps. Des sous-programmes, tels que *function* et *task*, sont déclarés à l'extérieur du module où ils sont appelés à la manière de C.

```

module logical_adder (I1, I2, O);

input I1, I2;

output O;

reg O;

always (I1 or I2)

begin

if (I1) O=1 else if (I2) O=1 else O=0;

end

endmodule

```

Figure 2.1 : Additionneur logique

```

module name component (inputs and outputs list);

input ..., ...; // list of inputs

output ..., ...; // list of outputs

reg ..., ...; // list of registers

wire ..., ...; // list of wire parameters

initial // block of initialization

begin

// instructions of initialization to be run once

end

always // block that are always running

begin

// instructions of always block

. . .

end

endmodule // the end of module name component

task name task // declaration of procedure (void function in C)

begin

... // task body

end

function name_function // declaration of function (type function in C)

begin

... // function body

end

```

Figure 2.2 : Structure générale d'un programme en Verilog

#### B. VHDL

VHDL («VHSIC Hardware Description Language») [12-26] est un langage de description de matériel selon la norme IEEE. Il est généralement utilisé pour modéliser, à différents niveaux d'abstraction, des composants et des systèmes numériques tels que des puces, des interfaces, des cartes, etc. Étant un standard IEEE, VHDL vient renforcer le développement, la simulation, la vérification, la synthèse et le test des designs matériels en permettant une description commune et compatible pour tous leurs outils respectifs.

Fortement typé, VHDL est conçu à base d'Ada. C'est un langage très puissant grâce à ses qualités de programmation moderne, à ses capacités d'implémenter des designs à grande échelle et à son aptitude à réutiliser des anciens designs. Dans la littérature, il y a suffisamment d'ouvrages récents dont [12-26], qui examinent la modélisation, la simulation et la synthèse à l'aide de du langage VHDL. Dans ce qui suit, nous présentons sommairement l'essentiel de ce langage.

La plus importante caractéristique du langage VHDL est sa faculté de séparer la spécification de l'interface (*entity*) de celle de son corps (*architecture*). Ceci permet à une seule interface d'avoir plusieurs implémentations de son corps. Le code VHDL pourrait être donc développé de manière modulaire. Aussi, de nouvelles unités élémentaires conçues en VHDL peuvent-elles enrichir la librairie de VHDL en les stockant dans des modules connus sous le nom de *packages*. Ces derniers sont éventuellement réutilisés dans des designs ultérieurs. Voici les différentes composantes d'un design en VHDL:

- *Entity*: Elle décrit l'interface d'un composant, toutefois elle est indépendante de son implémentation. Dans cette unité, sont déclarés tous les ports d'entrée et de sortie d'où communique le composant avec son environnement.

- Architecture : Elle décrit une implémentation possible d'une entité déclarée. Cette architecture peut être réalisée selon trois styles différents : architectures structurelle,

comportementale et mixte. Le style comportemental comprend aussi deux sousstyles : algorithmique et orienté flux de données.

- Configuration: Elle relie les références de l'interface locale (entity) et de ses architectures aux unités préconçues de la librairie VHDL (prédéfinie ou enrichie par l'utilisateur). Plusieurs architectures pourront être associées à une même interface, alors la configuration s'avère indispensable pour identifier laquelle d'entre elles il faut utiliser lorsque l'interface est instantiée.

- *Package*: Il englobe des informations prédéfinies communes à plusieurs unités de design, telles que des composants préconçus, des fonctions, des types, des signaux, des constantes, etc. Un package en VHDL, comme en d'autres langages, cache les détails aux utilisateurs et permet la réutilisation du code VHDL.

#### 2.4. Synthèse

La synthèse est définie comme étant le processus de raffinage partant d'un modèle abstrait jusqu'à un modèle plus détaillé de plus bas niveau d'abstraction. Le raffinage prend en considération toutes les contraintes, que ce soit celles formulées par l'utilisateur ou celles émanant des règles de conception. Durant ce processus, des paramètres de performance sont optimisés pour satisfaire les contraintes mises en jeu. Parmi ces paramètres, nous en citons : la capacité de traitement (« throuput rate »), la latence (« latency »), le cycle de l'horloge (« clock cycle »), la surface du circuit (« circuit area »), la puissance (« power »), la testabilité, et ainsi de suite. On distingue dans la synthèse trois types [17] : la synthèse comportementale, la synthèse logique et la synthèse au niveau circuit.

## 2.5. Vérification par simulation et test

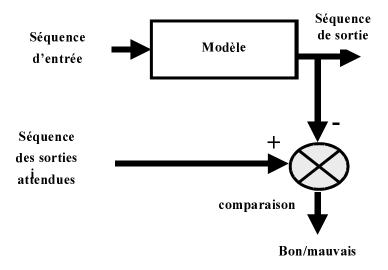

La simulation est l'approche la plus répandue pour la vérification des systèmes numériques. Ce type de vérification est basé sur un modèle HDL du système étudié. Ce modèle décrit le comportement global ou partiel du système. Il est stimulé par une série de vecteurs de test et les résultats obtenus (à ses sorties) sont comparés avec des valeurs prévues dans les mêmes conditions de la manipulation.

L'avantage majeur de la vérification par simulation apparaît dans le fait qu'elle ne nécessite pas un prototype matériel et qu'elle est souvent implémentée par les outils de conception assistée par ordinateur (« CAD tools »). Cependant, cette méthodologie est gourmande en terme de temps. En outre, elle requiert une génération de stimuli, les appliquer à l'entrée du système et ensuite en entamer la tâche de vérification.

La communauté du test a défini les niveaux d'abstraction suivants :

- Le *niveau système*, où le système numérique est présenté comme des unités échangeant des messages entre elles (chaque unité est une sorte de boîte noire dont le comportement est décrit par ses entrées-sorties).

- Le *niveau processeur*, où le système est vu comme un ensemble de programmes et de structures de données.

- Le *niveau instruction*, où le système est considéré comme une unité capable d'exécuter un ensemble d'instructions ayant un effet sur un nombre de registres et de ports.

- Le *niveau registre*, où le système est perçu comme étant composé de deux parties : la partie de contrôle qui peut être décrite par une FSM ou par une structure logique aléatoire; la partie du chemin de données est constituée des unités fonctionnelles et des registres.

- Le *niveau logique*, où le système est vu comme une interconnexion de portes logiques et de bascules.

À chaque niveau d'abstraction, des suites de test sont éventuellement générées et différents aspects du système peuvent être simulés. Le modèle peut être compilé en un code objet qui est très efficace mais de moindre flexibilité que la simulation à événements. Actuellement, les environnements CAD utilisent une approche mixte qui fait un compromis entre l'efficacité et la flexibilité.

La simulation peut être aussi effectuée en étapes successives : Dans une première étape, la fonctionnalité du système est vérifiée sans se préoccuper des caractéristiques temporelles du design. Une fois que cette étape est accomplie et qu'un modèle structurel est automatiquement ou manuellement dérivé, les contraintes temporelles sont vérifiées. Différents modèles de « timing » sont

éventuellement utilisés. Le modèle « unit-delay » où chaque porte logique élémentaire fait un délai d'une unité de temps, est le modèle le plus simple et le plus rapide en terme de temps de simulation. Il donne une idée primaire sur la performance du système simulé. Il existe d'autres modèles plus élaborés qui tiennent compte aussi des raccords d'interconnexion et considèrent des délais plus exacts pour les portes logiques. De tels modèles sont plus précis en terme de performance globale du système, toutefois leur usage requiert des librairies spécifiques des différentes technologies et des environnements CAD sophistiqués.

#### 2.5.1. Modélisation des fautes

Un fonctionnement anormal observable d'un système est appelé une *erreur*. Une erreur est une conséquence d'une *faute* dans le système. Les fautes peuvent résulter des causes suivantes :

- *erreurs de conception* telles que des spécifications incomplètes, des contradictions entre les différents niveaux d'abstraction ou des violations des règles de conception.

- erreurs de fabrication telles que des connexions incorrectes ou des composants non convenables.

- défauts de fabrication lors du processus de fabrication.

- défaillances physiques résultant du vieillissement des composants et des facteurs environnementaux.

Les fautes peuvent être permanentes, intermittentes ou transitoires. Il est très difficile d'examiner toutes ces sortes de fautes dans un modèle abstrait du système sous test; par exemple, si nous avons un modèle au niveau porte logique, alors il est très compliqué voire impossible de modéliser des erreurs d'alignement de la gaufre (« mask alignment error »). Les fautes logiques représentent des effets des fautes physiques. L'ensemble des fautes logiques possibles est appelé un modèle de fautes.

Le modèle des fautes suppose que, dans un circuit combinatoire, chaque ligne peut être « collée » de façon permanente à une des valeurs logiques 0 ou 1. On dit que les fautes sont de types collé-0 ou collé-1. Si un circuit donné possède n lignes, chacune d'elles peut soit fonctionner correctement, soit être collée-0, soit être collée-

1, alors le nombre de tous les cas possibles à considérer est 3<sup>n</sup>-1 [33]. Dans le cas où seulement une ligne serait responsable d'induire le circuit en faute, le modèle est dit « collé à une seule faute », autrement il est dit « collé à fautes multiples ». Détecter une faute f dans un circuit combinatoire est un problème NP-complet [34, 35, 36]. Le modèle « collé à une seule faute » est le plus utilisé grâce au fait qu'il est simple à manipuler et indépendant des technologies. De plus, il a été démontré expérimentalement que la majorité des circuits ayant réussi les suites de test conçues pour un modèle « collé à une seule faute», sont des circuits sans fautes (ils ne contiennent pas d'autres fautes non classiques) [33]. Ce modèle a été étendu aux niveaux élevés d'abstraction comme le RTL. D'autres modèles de fautes ont été proposés, tels que les fautes du pont et les fautes du délai [33].

#### 2.5.2. Techniques de simulation des fautes

L'objectif de la simulation des fautes est d'évaluer efficacement la couverture d'une séquence de test. La couverture peut être définie comme le pourcentage de fautes couvertes par la séquence, étant donné un modèle de faute.

La simulation des fautes, de manière séquentielle, transforme le modèle du circuit sans fautes C pour représenter le circuit fautif  $C_f$  résultant d'une faute f. Avec cette technique, une seule faute est simulée à la fois, d'où le processus doit être répété pour chaque faute; ceci le rend inapplicable pour des circuits réels. La simulation des fautes parallèles simule simultanément le circuit bon et un nombre de circuits fautifs. Les réponses de tous ces circuits aux même vecteurs de test sont emmagasinées dans des cases-mémoires contiguës. La simulation des fautes déductives, basée sur la simulation du bon circuit, déduit le comportement de tous les circuits fautifs théoriques; seul un sous-ensemble de ces derniers est examiné à cause de la limitation de mémoire. La simulation des fautes concurrentes observe si des résultats des circuits fautifs concordent ou pas avec ceux du bon circuit (sain); et elle continue l'analyse juste pour les circuits dont les sorties sont incorrectes [33].

#### 2.5.3. Génération automatique des patrons de test

La génération automatique de tests est une importante tâche dans le flux de conception. Elle est très difficile parce qu'elle est un problème NP-dur même pour les circuits combinatoires sous le modèle « collé à une seule faute ». Les outils automatiques s'intéressent aussi bien aux circuits combinatoires qu'aux parties combinatoires des circuits séquentiels. Les techniques de la conception prévoyant la testabilité, comme nous allons le voir dans la section 2.5.5, réduisent le problème de test des circuits séquentiels à un problème de test des circuits combinatoires. Comme il a été mentionné précédemment, des techniques de moindre coût telles que la génération aléatoire de test suivie de la simulation de fautes, peuvent être utilisées en première étape, ensuite viennent les méthodes déterministes pour élargir la couverture. Parmi les méthodes déterministes les plus connues dans le domaine de la génération de test pour les circuits combinatoires sous un modèle « collé à une seule faute », nous citons (à titre d'exemple) le D-algorithme [37], PODEM (« Path-Oriented Decision Making ») [38] et FAN (« FANout-Oriented Test Generation ») [39].

#### 2.5.4. Test fonctionnel

Un test fonctionnel teste une implémentation contre sa spécification fonctionnelle. C'est un test de conformité entre l'implémentation et sa spécification. Il est fréquemment appliqué aux niveaux d'abstraction plus élevés que le niveau porte. Le diagnostic, processus de détection et de localisation des erreurs, est plus important à ces niveaux parce que les erreurs sont de type *erreurs de conception* qui doivent être corrigées avant de procéder à la suite.

Les techniques du test exhaustives ne sont rien d'autre qu'une illustration du test fonctionnel appliqué aux petits circuits combinatoires et séquentiels. Les techniques du test pseudo – exhaustives sont applicables aux circuits qui peuvent être répartis en blocs caractérisés chacun par ses entrées-sorties; ces blocs doivent être de petite taille pour pouvoir les tester exhaustivement. Les circuits logiques itératifs organisés en table (ILAs) sont les candidats parfaits pour le cas du test pseudo-

exhaustif; ils peuvent être perçus comme étant une interconnexion régulière de cellules identiques (par exemple, un additionneur *ripple-carry*) [33].

#### 2.5.5. Conception prévoyant la testabilité (DFT)

La testabilité est une mesure de la facilité avec laquelle on peut tester un circuit ou un système. Elle prend en compte le coût de la génération des suites de test et leur application au système à tester. Le coût et le temps associés au test peuvent souvent dépasser ceux des autres tâches requises durant l'accomplissement de la conception. L'objectif principal du DFT consiste en la réduction de ces paramètres. En résumé, la testabilité d'un circuit est influencée par trois facteurs :

- *La contrôlabilité*, elle mesure le degré de facilité d'affecter une valeur spécifique à n'importe quel nœud dans le système.

- *L'observabilité*, elle mesure le degré de facilité de déduire la valeur de n'importe quel nœud du système juste en observant ses sorties.

- *La prédictibilité*, elle mesure le degré de facilité d'obtenir la valeur d'une sortie en réponse à une application éventuelle d'une valeur donnée à l'entrée du système.

Plusieurs techniques ad hoc de DFT ont été développées et elles sont bien résumées dans la référence [33]; ces techniques en général tentent d'atteindre les objectifs suivants :

- Améliorer l'observabilité et la contrôlabilité en rendant possible l'accès direct aux points d'observation (sorties et autres) et aux points de contrôle (entrées et autres).

- Faciliter l'initialisation des circuits en prévoyant une entrée *RESET* par exemple.

- Permettre la désactivation des horloges internes durant la campagne de test.

- Faciliter la répartition d'un circuit en plusieurs sous-circuits lors de la génération de test.

- Éviter l'usage de la logique redondante.

- Développer ou fournir une logique capable de casser les boucles de feedback.

La technique de conception basée sur le test (« scan-based design ») constitue l'une des techniques DFT les plus réussies parce qu'elle possède de bonnes caractéristiques en termes de temps de test, de borne supérieure d'aire, et de pattes I/O réservées au test. Elle est basée sur l'usage des registres de « scan » capables d'effectuer des opérations de décalage et de chargement parallèle [33]. LSSD appartient à cette classe de techniques; elle est utilisée dans des architectures IBM [40]. Des standards de DFT ont été développés aussi pour servir au test au niveau des cartes (« board level »); nous mentionnons à titre d'exemple le « JTAG Boundary Scan standard » [41] et le standard IEEE 1149.1 [42].

Nous concluons cette section en citant les techniques de compression qui consistent à compresser la réponse du circuit dans ce qu'on appelle une signature, et l'autotest intégré (BIST) qui appartient à une autre classe de techniques; pour avoir plus d'explications sur ces techniques, le lecteur est invité à consulter la référence [33].

#### 2.6. Vérification formelle du matériel

La vérification est une activité de conception très importante. Comme le nombre de portes croit très rapidement et la complexité des circuits intègres devient de plus en plus exigeante, les défis à concevoir un circuit intégré sont sans précédents. Les approches de vérification classiques (simulation et test) ne sont pas très efficaces pour des systèmes complexes. C'est très coûteux, voire impossible, de tester ou de simuler toutes les entrées possibles d'un système dont le nombre d'entrées est excessivement grand. La simulation et le test ne garantissent pas un design sans erreurs, d'autant plus si le design fait intervenir des boîtes noires telles que les blocs à propriétés intellectuelles (« Bloc-based design (BBD) » ou « Intellectual Property Blocs (IPs) »).

Les techniques de la vérification formelle [36, 43] cherche à démontrer si un design est correct ou non sans avoir besoin d'une simulation exhaustive. La vérification formelle d'un système se fait à la manière des preuves mathématiques des théorèmes, sans se soucier des valeurs des entrées.

Une implémentation représente le design du système qui devrait être vérifié afin de savoir s'il (le design) correspond ou pas à sa description initiale

(spécification). La spécification représente les propriétés auxquelles se réfère le processus de vérification pour conclure de la conformité d'un système. Elle peut être exprimée de différentes manières telles qu'une description comportementale, une description structurelle abstraite ou un ensemble de propriétés temporelles. Du fait que le raisonnement est formel, un formalisme est indispensable pour exprimer les trois entités: l'implémentation, la spécification et la relation entre elles. Les représentations d'une implémentation peuvent être des réseaux de transistors/portes, des automates à états finis, une description en logique, et ainsi de suite [17]. Les formalismes utilisés pour représenter des spécifications sont classifiés en (*i*) automates de logique et (*ii*) théorie des langages. La logique en question inclut la logique propositionnelle, la logique des prédicats de premier ordre, la logique d'ordre élevé et la logique modale (la logique temporelle, etc.) [19, 44].

Les méthodes de la vérification formelle peuvent être classées en deux grandes catégories : (i) la vérification interactive utilisant des 'prouveurs' de théorèmes (« theorem-prover ») et (ii) la vérification basée sur l'énumération des états des FSMs.

#### 2.6.1. « Model-Checking »

Les méthodes « model-checking » et « equivalence checking » font partie de la catégorie de vérification basée sur des machines à états finis (FSM). Elles requièrent une exploration exhaustive de l'espace des états du modèle. Malheureusement, cette exploration provoque, dans le cas des systèmes de grande taille, un problème d'explosion d'états. Ceci est donc une limitation de l'usage de ces méthodes. Pour en remédier, des tentatives d'amélioration ont été proposées dans les références suivantes [45-50]. Pour alléger le problème d'explosion, McMillan propose dans [45] de ne pas représenter explicitement les états du modèle; le groupe de Bryant a proposé le ROBDD (« Reduced Ordered Binary Decision Diagrams ») [46] pour ordonner et réduire les digrammes de décision binaires. Cette technique est connue sous le nom de « symbolic model checking » du fait que des variables symboliques sont utilisées pour représenter les états du système au lieu des variables numériques. Bien que l'emploi du ROBDD pour explorer implicitement l'espace des

états, ait élargi le domaine d'application de l'approche « model checking », cette dernière demeure inadéquate pour la vérification des circuits à grand chemin de données. Ceci est dû au fait que les ROBDDs sont considérés au niveau logique booléen, ce qui veut dire qu'une variable individuelle est nécessaire pour chaque bit d'une donnée; donc, le problème d'explosion d'états persiste encore pour les circuits à grand chemin de données. Par contre les ROBDDs se prêtent bien à la vérification des chemins de contrôle. Alors, des méthodes plus efficaces doivent être développées pour vérifier aussi bien les chemins de données que leurs interactions avec les chemins de contrôle d'un design. La technique de MDG (« Multiway Decision Graphs ») [47, 48] est proposée dans ce cadre, cependant son utilisation reste très limitée.

La technique de « model checking » a été appliquée pour vérifier automatiquement des designs de complexité significative tels que la vérification du protocole de cohérence des caches d'un système multiprocesseur [45, 51].

L'avantage le plus important du « model checking » est que cette technique peut être complètement automatique. Aussi, se prête-t-elle bien à la vérification du contrôle des systèmes. Cependant, son inconvénient est qu'elle est plus restrictive en application et faible en vérification hiérarchique en comparaison avec le « theorem-proving ».

#### 2.6.2. « Theorem-Proving »

L'approche la plus générale de vérification est de formuler les conditions de conformité d'un système comme des théorèmes à démontrer, et de générer ensuite mécaniquement des preuves pour ces théorèmes en utilisant un outil dédié à ce genre de tâches. La technique de « theorem-proving » utilise des formalismes puissants tels que la logique d'ordre élevé [52], qui permettent de postuler le problème de vérification à différents niveaux d'abstraction. Cette approche a connu des succès significatifs dans la vérification des designs des microprocesseurs [44, 53]. Cependant, la vérification basée sur cette technique est moins automatique [52, 54].

De nos jours, la majorité des systèmes de « theorem-proving » sont semiautomatiques et exigent plus d'efforts du côté de l'utilisateur afin de développer des

spécifications pour chaque composant et à superviser le processus d'inférence. D'où, seuls les experts et les avertis sont capables d'utiliser cette technique sans trop de peine.

#### 2.7. Conclusion

Nous avons présenté au sein de ce chapitre un aperçu global sur les techniques de conception, telles que la modélisation, la synthèse, la simulation, le test et la vérification formelle. Pour surmonter les limitations et faire face aux complexités excessivement ascendantes des systèmes, de nouvelles approches combinant différentes méthodes classiques surgissent dans le champ de la micro-électronique; le codesign L/M, la réutilisation de design, le développement des modèles et des blocs matériels à propriétés intellectuelles, la coverification L/M et la révision des méthodes traditionnelles semblent être le point de visée auquel vont concourir les intérêts futurs dans le domaine de conception et de vérification des systèmes numériques.

## Chapitre 3

# Introduction au codesign et à la covérification des systèmes intégrés

#### 3.1. Introduction

La covérification L/M d'un système intégré est une nouvelle perception de la vérification de ses deux parties constituantes au fur et à mesure que sa conception se réalise. Elle revêt un intérêt potentiel dans le monde des circuits intégrés dédiés à des applications spécifiques (ASICs). L'utilisation de ces derniers est très abondante mais la maîtrise de leur complexité se complique davantage de jour en jour, ce qui explique la demande pressante pour le développement d'outils puissants pour la conception, la vérification et la réalisation de tels systèmes. De nombreuses tentatives académiques et industrielles n'arrivant pas à satisfaire les exigences de qualité et d'efficacité, ont fait l'objet des articles suivants [36, 51, 61-71].

Le reste de ce chapitre est organisé comme suit : à la section 3.2, nous exposons le problème de la covérification d'une manière générale, puis à la section 3.3, nous examinons brièvement le processus du codesign L/M. Nous faisons un survol des principales techniques de covérification dans la section 3.4 tout en