**IFT 1225 - Examen final**

Nom: \_\_\_\_\_ Login: \_\_\_\_\_

Signature: \_\_\_\_\_ Code perm.: \_\_\_\_\_

**Directives:**

- Durée de l'examen: 3 heures.

- Toute documentation (papier) permise.

- Calculatrices permises.

- Répondre sur les feuilles mêmes du questionnaire.

- Le barème est indiqué entre parenthèses. (Total possible: 108)

1. Soit la routine de traitement d'interruption suivante, en assembleur SRC :

```

.org 20h

addi r30, r30, -4    ; Espace sur la pile pour sauver l'état

st   r0, 0(r30)

la   r0, int2

br   r0                 ; Branche à la routine de service pour l'interruption

.org 1000h

int2: een

ld   r0, compteur

addi r0, r0, 1      ; Incrémente le compteur

st   r0, compteur

edi

ld   r0, 0(r30)

addi r30, r30, 4

rfi

compteur: .dc 0

```

Cette routine compte le nombre d'interruptions de type 2 qui sont envoyées au processeur.

- a. (5 points) Dites pourquoi cette routine ne fonctionne pas s'il se produit une interruption d'un autre type pendant son traitement.

- b. (7 points) Dites pourquoi cette routine peut ne pas fonctionner s'il se produit une autre interruption de type 2 pendant son traitement, même si on corrige ce qui est en 'a'.

2. Soit un système avec une mémoire vive (physique) de 32MB et une mémoire virtuelle de 128MB. Pour diminuer le nombre d'accès disque, le système utilise le « write-back » (écriture au remplacement, seulement si la page a été modifiée). Le système a un noyau de 16MB qui doit toujours se trouver en mémoire physique, contenant entre autre la table de pages et les routines utilisées pour la gestion des fautes de page. Sur le processeur utilisé, les adresses virtuelles sont de 32bits, les pages sont de 4KB, la table de pages est à un seul niveau et la mémoire est adressée en bytes.

- a. (5 points) Quelle est la taille maximale de mémoire virtuelle qu'on peut avoir sur ce processeur?

-

- b. (5 points) Quelle est la taille de la table de pages (nombre d'entrées)?

-

- c. (7 points) Quel est l'espace disque utilisé par ce système comme mémoire? (espace minimal qui respecte tous les points de l'énoncé)

-

3. (7 points) La traduction d'adresse faite par le MMU permet de ne pas avoir de fragmentation externe, mais la taille des pages fait de la fragmentation interne. Dites très brièvement ce que sont la fragmentation interne et la fragmentation externe.

4. Soit une mémoire cache associative par ensembles avec 2 ensembles de 2 lignes, chaque ligne ayant un seul byte. Au départ la cache est vide, puis on fait les accès suivants (R pour lecture, W pour écriture, avec l'adresse à côté) : R0, R1, R2, R4, W0, W1, W4, R6, R0. La cache utilise la politique LRU et utilise le « write-back » et le « write-allocate » (puisque une ligne ne contient qu'un byte, aucune lecture mémoire est faite lors d'une écriture).

- (5 points) Quel est le nombre de défaut d'accès? \_\_\_\_\_

- (5 points) Quel est le nombre de lectures en mémoire principale? \_\_\_\_\_

- (5 points) Quel est le nombre d'écritures en mémoire principale? \_\_\_\_\_

- (5 points) Quels sont les tags dans la cache après ces accès? (le tag de chaque ligne)

Ensemble0{ \_\_\_\_   \_\_\_\_ } Ensemble1{ \_\_\_\_   \_\_\_\_ }

5. (5 Points) Soit une mémoire cache de 8KB, associative par ensembles de 4 lignes et avec des lignes de 16 bytes. L'adresse mémoire étant de 20 bits (adressée en bytes), comment est divisée cette adresse en Tag, Set et Byte ?

Tag:\_\_\_\_\_ Set:\_\_\_\_\_ Byte:\_\_\_\_\_

6. (10 points) Soit un ordinateur ayant un « DMA » et une cache branchés sur le même bus mémoire. La cache regarde ce qui se passe sur le bus, lorsque ce n'est pas elle qui l'utilise, pour savoir si quelqu'un d'autre modifie des données en mémoire qui se trouvent aussi dans la cache. Lorsque le « DMA » écrit en mémoire à une adresse qui se trouve dans la cache, la cache peut soit invalider la ligne, soit écrire la nouvelle donnée dans la cache en même temps que l'écriture se fait en mémoire. Donnez un avantage et un inconvénient (sur la performance) d'écrire aussi dans la cache plutôt que d'invalider la ligne.

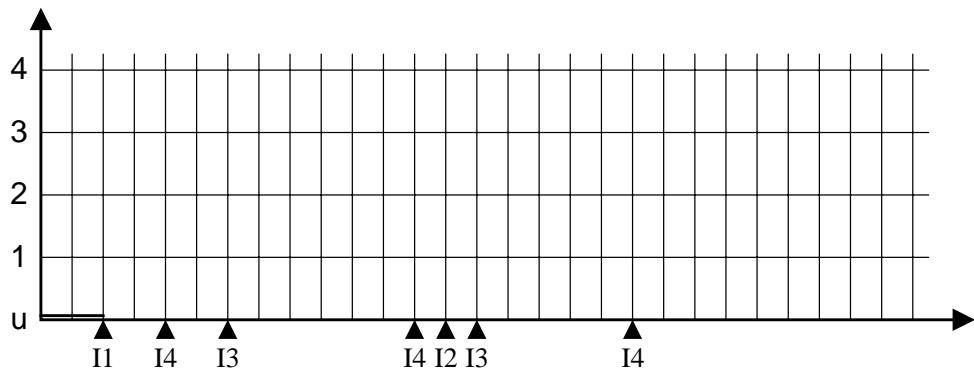

7. (10 points) Les interruptions I1-I4 arrivent aux moments indiqués par le diagramme ci-dessous. Les routines de service durent toutes 3 unitées de temps.

Complétez le diagramme pour indiquer quelle routine sera en exécution à quel moment (les unités de temps correspondent aux lignes verticales). Les interruptions de priorité 4 sont plus prioritaires que celles de priorité 3, etc. Les routines (sauf celle pour I2) permettent les interruptions imbriquées, en inhibant seulement les interruptions de priorité inférieure. La routine d'interruption I2 inhibe toutes les interruptions.

8. Supposons que le temps pour accéder à une cache niveau 2 est de 5ns et que le temps pour accéder à la mémoire est de 50ns. Sur le programme test, le taux de succès de cette cache est de 80%. Le processeur utilisé est un RISC à 400MHz.

- a. (5 points) Quel est le temps d'accès effectif lors d'un défaut d'accès à la cache niveau 1?

\_\_\_\_\_ ns

- b. (7 points) Avec une cache niveau 2 qui a un temps d'accès de 2,5ns, quel devrait être le taux de succès pour que le système ait la même performance?

\_\_\_\_\_ %

- c. (3 points) Si on avait simplement spécifié « cache » plutôt que « cache niveau 2 », qu'est-ce qui serait inconsistant dans l'énoncé?

9. Communications (2 points chaque) :

- a. Codez la série de bits 10110001 en NRZI.

- b. Lors du transfert d'une musique, pourquoi Internet n'est pas bon pour l'écouter à mesure qu'elle arrive ?

- c. Pourquoi, sur une radio, le FM donne une meilleure qualité de son que le AM?

- d. Quel est l'avantage d'utiliser une topologie en anneau pour interconnecter les processeurs dans une ordinateur parallèle?

- e. Pourquoi utilise-t-on un bus plutôt qu'une étoile pour inter-connecter les différents périphériques, mémoires et processeur dans une ordinateur?

- f. Dans le protocole Ethernet pour la transmission sur un bus, pourquoi est-il nécessaire d'utiliser un nombre alléatoire?