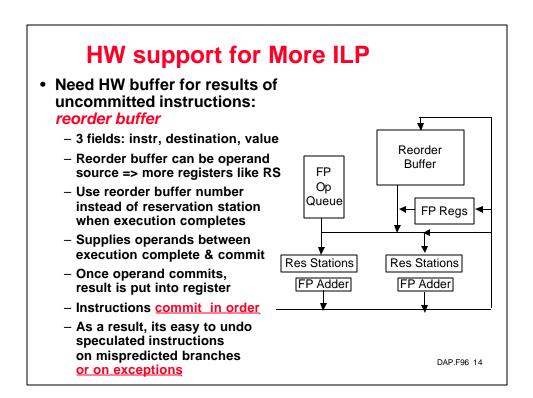

If reservation station <u>and reorder buffer slot</u> free, issue instr & send operands <u>& reorder buffer no. for</u> <u>destination</u> (this stage sometimes called "dispatch")

#### **2. Execution**—operate on operands (EX)

When both operands ready then execute; if not ready, watch CDB for result; when both in reservation station, execute; checks RAW (sometimes called "issue")

#### 3. Write result—finish execution (WB)

Write on Common Data Bus to all awaiting FUs <u>& reorder buffer;</u> mark reservation station available.

4. <u>Commit</u>—update register with reorder result <u>When instr. at head of reorder buffer & result present</u>, <u>update register with result (or store to memory) and</u>

remove instr from reorder buffer. Mispredicted branch DAP.F96 15 flushes reorder buffer (sometimes called "graduation")

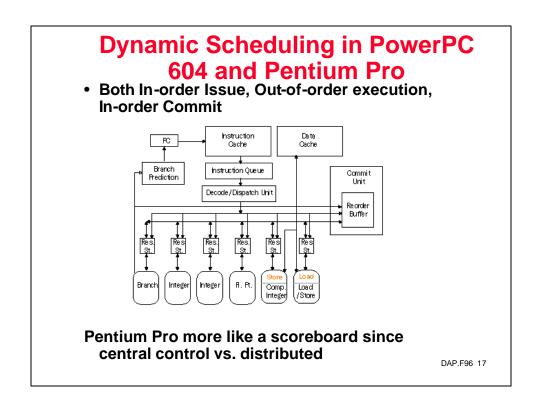

| Dynamic Scheduling in                          |            |  |  |  |

|------------------------------------------------|------------|--|--|--|

| PowerPC 604 and Pentium                        | Pro        |  |  |  |

| Parameter PPC                                  | PPro       |  |  |  |

| Max. instructions issued/clock 4               | 3          |  |  |  |

| Max. instr. complete exec./clock 6             | 5          |  |  |  |

| Max. instr. commited/clock 6                   | 3          |  |  |  |

| Window (Instrs in reorder buffer) 16           | 40         |  |  |  |

| Number of reservations stations 12             | 20         |  |  |  |

| Number of rename registers 8int/12FP           | 40         |  |  |  |

| No. integer functional units (FUs) 2           | 2          |  |  |  |

| No. floating point FUs 1                       | 1          |  |  |  |

| No. branch FUs 1                               | 1          |  |  |  |

| No. complex integer FUs 1                      | 0          |  |  |  |

|                                                | d +1 store |  |  |  |

| Q: How pipeline 1 to 17 byte x86 instructions? |            |  |  |  |

# **Dynamic Scheduling in Pentium Pro**

- PPro doesn't pipeline 80x86 instructions

- PPro decode unit translates the Intel instructions into 72-bit micro-operations (- DLX)

- Sends micro-operations to reorder buffer & reservation stations

- Takes 1 clock cycle to determine length of 80x86 instructions + 2 more to create the micro-operations

- •12-14 clocks in total pipeline (- 3 state machines)

- Many instructions translate to 1 to 4 micro-operations

- Complex 80x86 instructions are executed by a conventional microprogram (8K x 72 bits) that issues long sequences of micro-operations

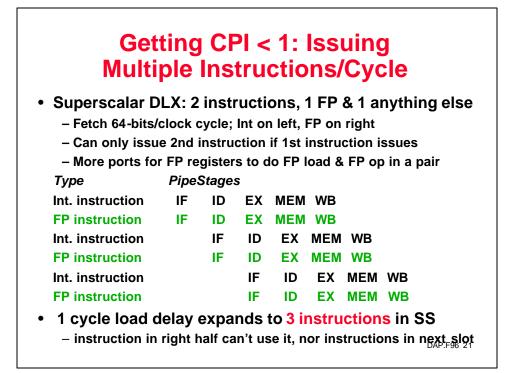

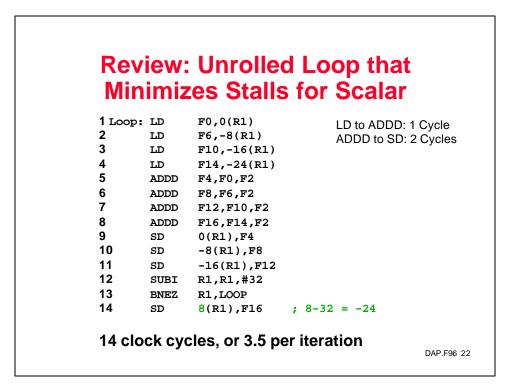

| L      | oop Unrollii        | ng in Supers        | scalar          |

|--------|---------------------|---------------------|-----------------|

|        | Integer instruction | FP instruction      | Clock cycle     |

| Loop:  | LD F0.0(R1)         |                     | 1               |

|        | LD F6,-8(R1)        |                     | 2               |

|        | LD F10,-16(R1)      | ADDDF4F0F2          | 3               |

|        | LD F14,-24(R1)      | ADDD F8,F6,F2       | 4               |

|        | LD F18,-32(R1)      | ADDD F12,F10,F2     | 5               |

|        | SD 0(R1),F4         | ADDD F16,F14,F2     | 6               |

|        | SD -8(R1),F8        | ADDD F20,F18,F2     | 7               |

|        | SD -16(R1),F12      |                     | 8               |

|        | SD -24(R1),F16      |                     | 9               |

|        | SUBI R1,R1,#40      |                     | 10              |

|        | BNEZ R1,LOOP        |                     | 11              |

|        | SD -32(R1),F20      |                     | 12              |

| • Unr  | olled 5 times to a  | void delays (+1 du  | ue to SS)       |

| • 12 0 | locks, or 2.4 cloc  | ks per iteration (1 | .5X) DAP.F96 23 |

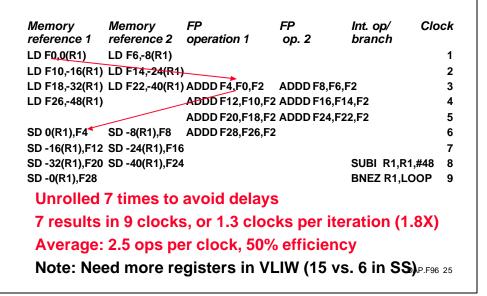

# Loop Unrolling in VLIW

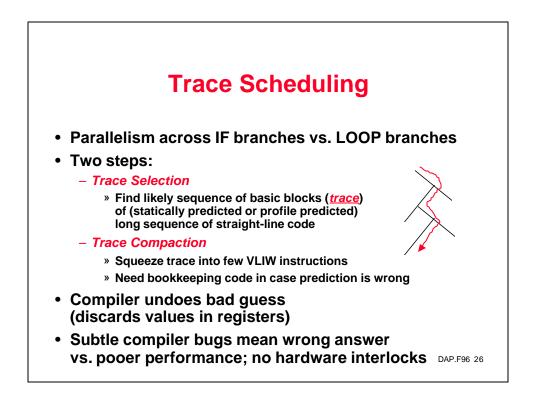

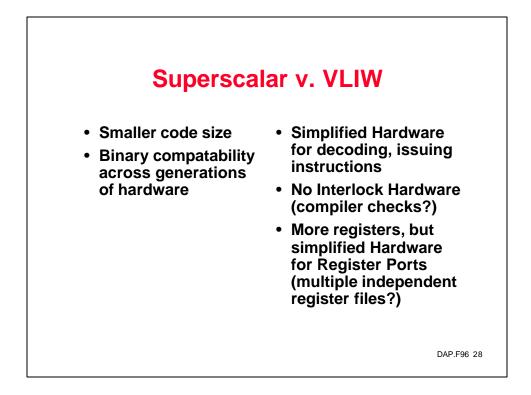

### Advantages of HW (Tomasulo) vs. SW (VLIW) Speculation

- HW determines address conflicts

- HW better branch prediction

- HW maintains precise exception model

- HW does not execute bookkeeping instructions

- Works across multiple implementations

- SW speculation is much easier for HW design

### Intel/HP "Explicitly Parallel Instruction Computer (EPIC)"

- 3 Instructions in 128 bit "groups"; field determines if instructions dependent or independent

- Smaller code size than old VLIW, larger than x86/RISC

- Groups can be linked to show independence > 3 instr

- 64 integer registers + 64 floating point registers – Not separate filesper functional unit as in old VLIW

- Hardware checks dependencies (interlocks => binary compatibility over time)

- Predicated execution (select 1 out of 64 1-bit flags)

=> 40% fewer mispredictions?

- <u>IA-64</u>: name of instruction set architecture; EPIC is type

- <u>Merced</u> is name of first implementation (1999/2000?)

- LIW = EPIC?

| Iteratio | on Instructions           | Issues   | Executes    | Writes result  |

|----------|---------------------------|----------|-------------|----------------|

| no.      |                           | cloc     | k-cycle nun | nber           |

| 1        | LD 🔞 (R1)                 | 1        | 2           | 4              |

| 1        | ADDDF40F2                 | 1        | 5           | 8              |

| 1        | SD 0(R1), <mark>F4</mark> | 2        | 9           |                |

| 1        | SUBI R1,R1,#8             | 3        | 4           | 5              |

| 1        | BNEZ R1,LOOP              | 4        | 5           |                |

| 2        | LD F0,0(R1)               | 5        | 6           | 8              |

| 2        | ADDD F4,F0,F2             | 5        | 9           | 12             |

| 2        | SD 0(R1),F4               | 6        | 13          |                |

| 2        | SUBI R1,R1,#8             | 7        | 8           | 9              |

| 2        | <b>BNEZ R1,LOOP</b>       | 8        | 9           |                |

| - 4 cl   | ocks per iteratio         | n; only  | 1 FP inst   | r/iteration    |

| Bran     | ches, Decremen            | ts issue | s still tak | e 1 clock cvcl |

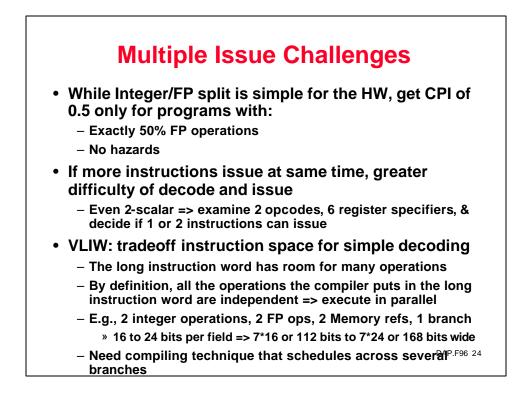

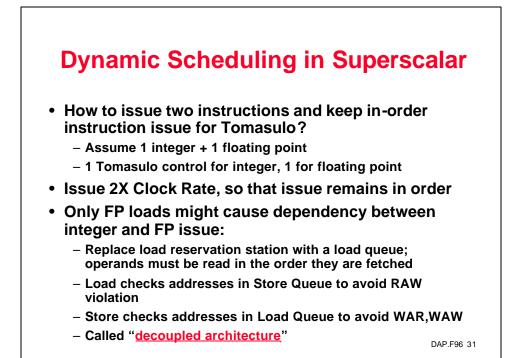

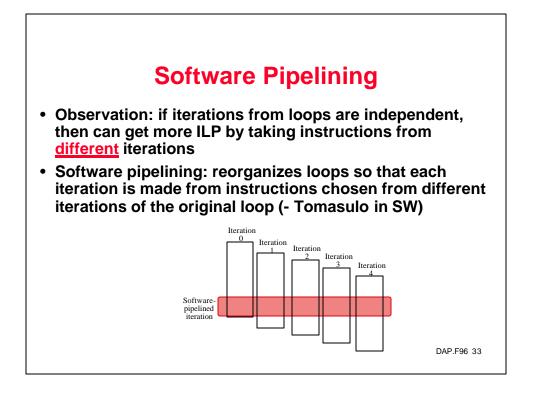

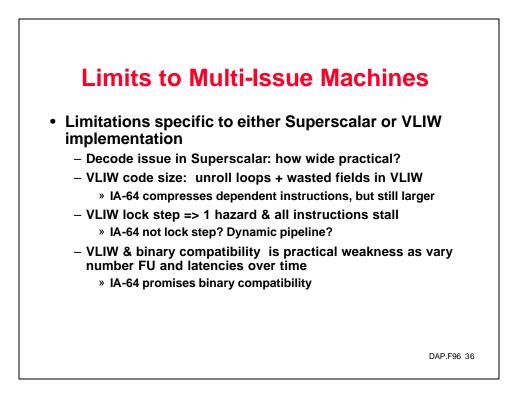

### **Limits to Multi-Issue Machines**

#### • Inherent limitations of ILP

- 1 branch in 5: How to keep a 5-way VLIW busy?

- Latencies of units: many operations must be scheduled

- Need about Pipeline Depth x No. Functional Units of independent operations to keep machines busy, e.g. 5 x 4 = 15–20 independent instructions?

- Difficulties in building HW

- Easy: More instruction bandwidth

- Easy: Duplicate FUs to get parallel execution

- Hard: Increase ports to Register File (bandwidth)

- » VLIW example needs 7 read and 3 write for Int. Reg. & 5 read and 3 write for FP reg

- Harder: Increase ports to memory (bandwidth)

- Decoding Superscalar and impact on clock rate, pipeline.F96 35 depth?

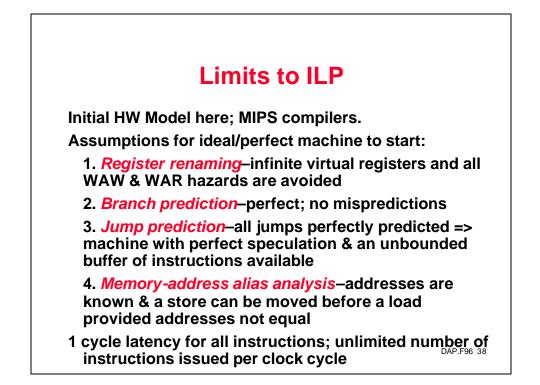

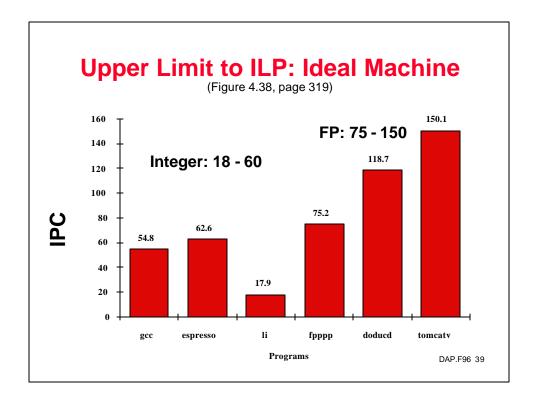

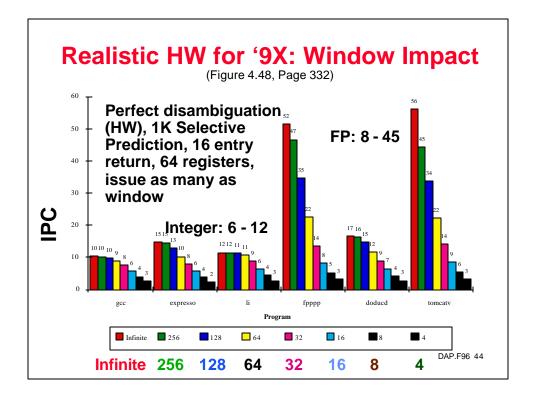

## Limits to ILP

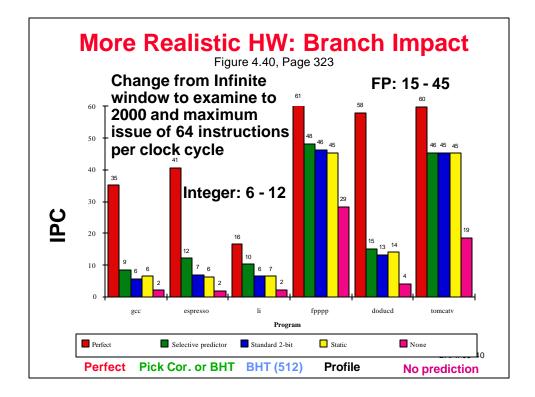

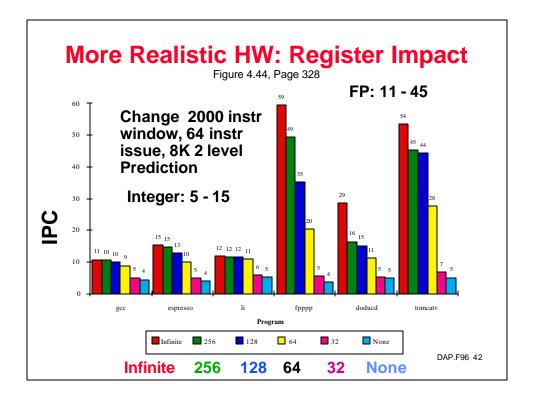

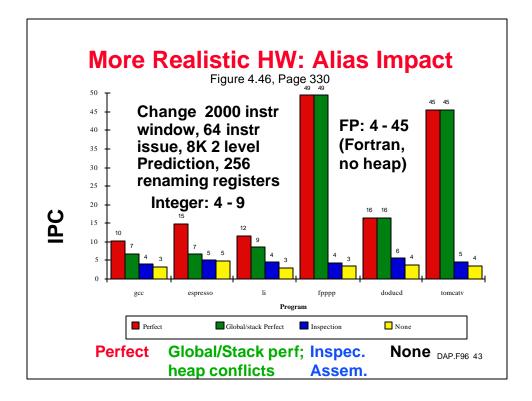

• Conflicting studies of amount of parallelism available in late 1980s and early 1990s. Different assumptions about:

- Benchmarks (vectorized Fortran FP vs. integer C programs)

- Hardware sophistication

- Compiler sophistication

- How much ILP is available using existing mechanisms with increasing HW budgets?

- Do we need to invent new HW/SW mechanisms to keep on processor performance curve?

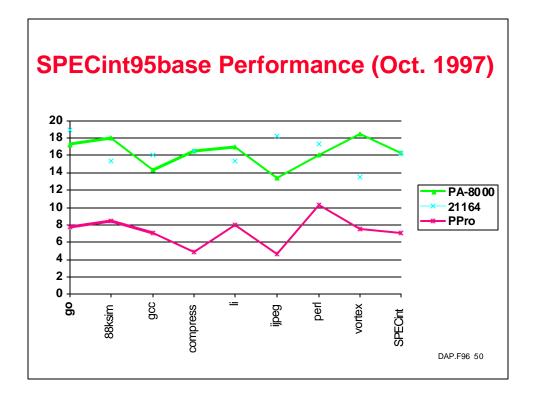

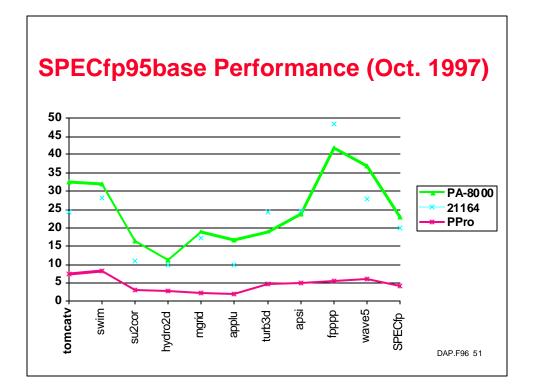

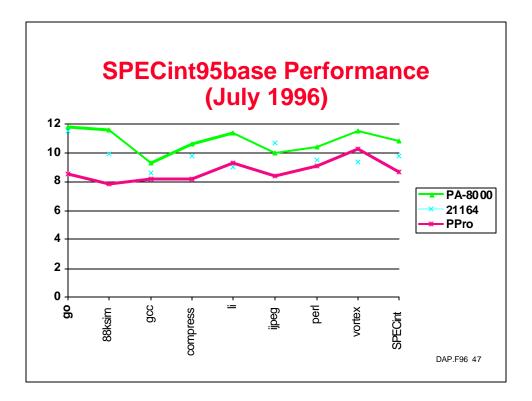

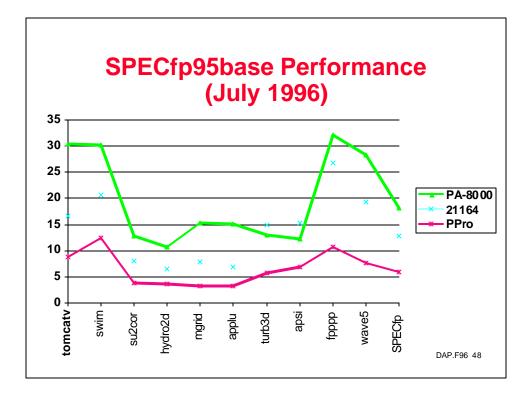

|            | 3 1996 Er    | a Machines     | 5          |

|------------|--------------|----------------|------------|

|            | Alpha 21164  | PPro           | HP PA-8000 |

| Year       | 1995         | 1995           | 1996       |

| Clock      | 400 MHz      | 200 MHz        | 180 MHz    |

| Cache      | 8K/8K/96K/2M | 8K/8K/0.5M     | 0/0/2M     |

| Issue rate | 2int+2FP     | 3 instr (x86)  | 4 instr    |

| Pipe stage | es 7-9       | 12-14          | 7-9        |

| Out-of-Ord | der 6 loads  | 40 instr (µop) | 56 instr   |

| Rename re  | egs none     | 40             | 56         |

|            |              |                |            |

# 3 1997 Era Machines

| Year<br>Clock<br>Cache<br>Issue rate<br>Pipe stage | Alpha 21164<br>1995<br>600 MHz ('97)<br>8K/8K/96K/2M<br>2int+2FP<br>es 7-9 | Pentium II<br>1996<br>300 MHz ('97)<br><u>16K/16K</u> /0.5M<br>3 instr (x86)<br>12-14 | HP PA-8000<br>1996<br>236 MHz ('97)<br>0/0/ <u>4M</u><br>4 instr<br>7-9 |

|----------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|                                                    | ler 6 loads                                                                | 12-14<br>40 instr (μορ)<br>40                                                         | 7-9<br>56 instr<br>56                                                   |

|                                                    |                                                                            |                                                                                       | DAP.F96 49                                                              |