| D    | eclarations and sequential construct                           | ts   |  |

|------|----------------------------------------------------------------|------|--|

|      | 1                                                              | Page |  |

| Lexi | cal elements                                                   | 2.1  |  |

| Decl | arations                                                       | 2.6  |  |

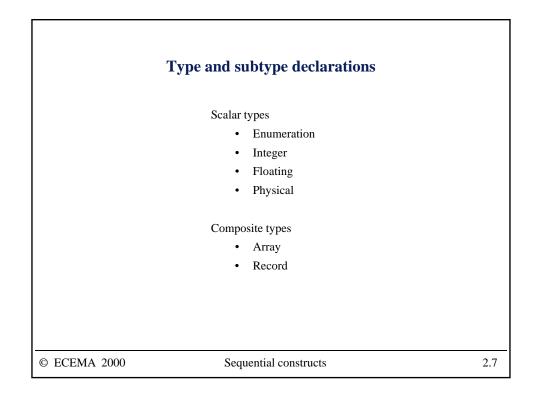

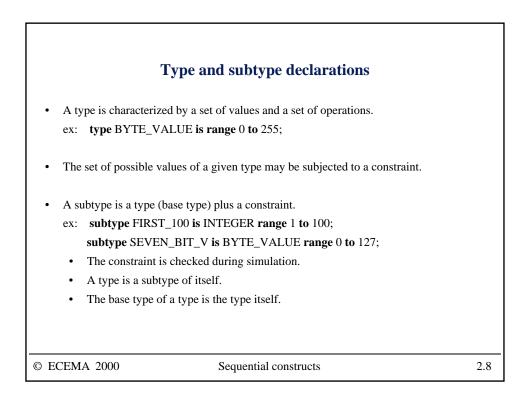

|      | <ul> <li>Type and subtype</li> </ul>                           | 2.7  |  |

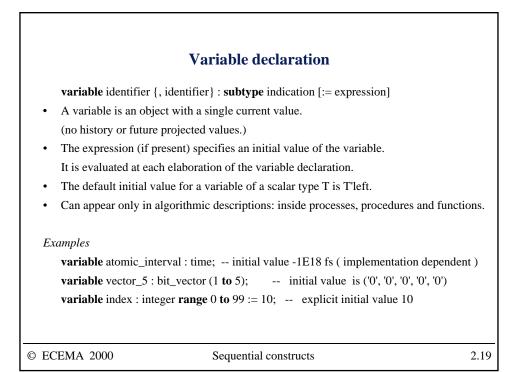

|      | <ul> <li>Constant, variable, signal</li> </ul>                 | 2.17 |  |

|      | – Entity                                                       | 2.21 |  |

|      | – Architecture                                                 | 2.26 |  |

| Expr | essions                                                        | 2.27 |  |

|      | - Operators                                                    | 2.28 |  |

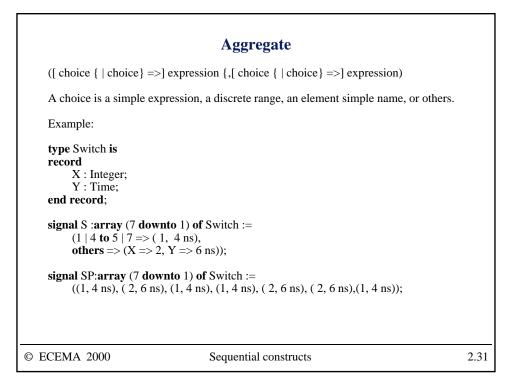

|      | <ul> <li>Aggregates</li> </ul>                                 | 2.31 |  |

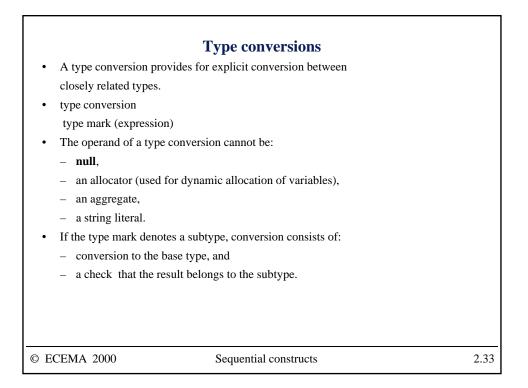

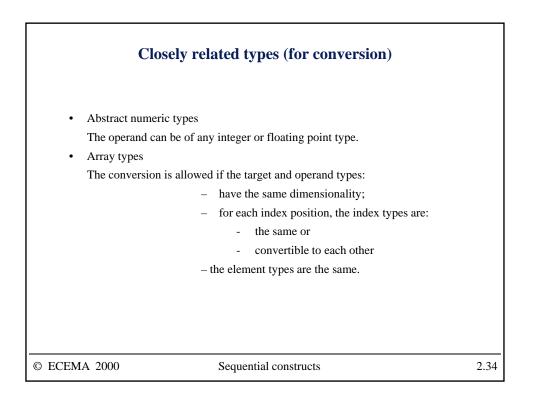

|      | <ul> <li>Qualified expressions and type conversions</li> </ul> | 2.32 |  |

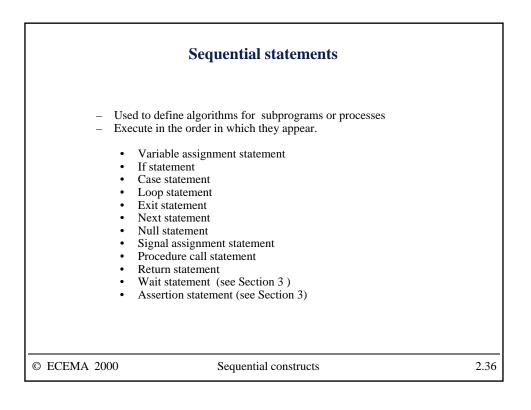

| Sequ | ential statements                                              | 2.36 |  |

| Subp | programs                                                       | 2.50 |  |

|                                        | Lexical elements                                      |     |

|----------------------------------------|-------------------------------------------------------|-----|

| Character set                          |                                                       |     |

| Letters: AZ, az                        |                                                       |     |

| Digits: 09                             |                                                       |     |

|                                        | \$ & '() +, / : ; < = > _   ! \$ % @ ? [ ] ^` { } ~ * |     |

| Space                                  |                                                       |     |

| An identifier is                       |                                                       |     |

| letter {[underlin                      | e] letter_or_digit}                                   |     |

| <ul> <li>not case sensitive</li> </ul> | /e                                                    |     |

|                                        |                                                       |     |

|                                        |                                                       |     |

|                                        |                                                       |     |

|                                        |                                                       |     |

| © ECEMA 2000                           | Sequential constructs                                 | 2.2 |

|                    |          | ]      | Literals  | (examp      | oles)    |               |     |

|--------------------|----------|--------|-----------|-------------|----------|---------------|-----|

| Decimal literals   |          |        |           |             |          |               |     |

| Integer literals:  | 12       | 0      | 1E6       | 123_450     | б        |               |     |

| Real literals:     | 2.0      | 0.0    | 0.456     | 3.1415      | 9_26     |               |     |

|                    | 1.34I    | E-12   | 1.0E+6    | 6.0231      | E24      |               |     |

| Based literals     |          |        |           |             |          |               |     |

| Integer literals o | of value | e 255: | 2#111     | 1_1111#     | 16#FF#   | 016#FF#       |     |

| Integer literals o | of value | e 224: | 16#E#     | E1          | 2#1110_0 | )000#         |     |

| Real literal of va | alue 40  | 95.0:  | 16#F.I    | FF#E2       | 2#1.1111 | _1111_111#E11 |     |

| Bit string-literal |          |        |           |             |          |               |     |

| X"FFF"             |          | = B"   | 1111_1111 | _1111"      |          |               |     |

| O"777"             |          | = B"   | 111_111_1 | 11"         |          |               |     |

| X"777"             |          | = B"   | 0111_0111 | _0111"      |          |               |     |

|                    |          |        |           |             |          |               |     |

|                    |          |        |           |             |          |               |     |

| © ECEMA 2000       |          |        | Sequent   | ial constru | icts     |               | 2.3 |

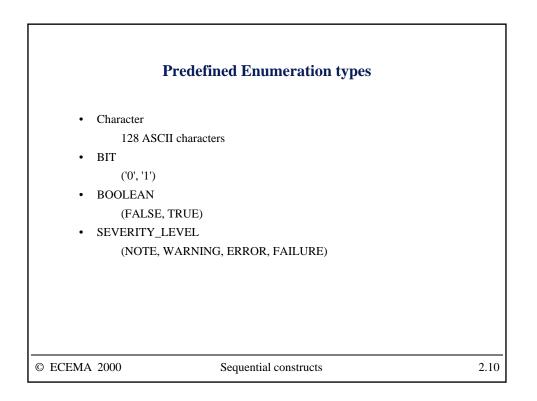

| Enumeration types                                                                                   |

|-----------------------------------------------------------------------------------------------------|

| Enumeration type definition                                                                         |

| == (enumeration literal { , enumeration literal})                                                   |

| Enumeration literal == identifier   character literal                                               |

| Encoded as bit vectors                                                                              |

| Examples                                                                                            |

| type TRANSITION is (H, L, R, F, U);                                                                 |

| Encoding: H:"000", L:"001", R:"010", F:"011", U:"100"                                               |

| <b>type</b> BIT <b>is</b> ('0', '1');                                                               |

| <b>type</b> LOGIC4 <b>is</b> ('X', '0', '1', 'Z'); '0' and '1' overloaded, type resolved by context |

| type MODE is (NORMAL, SCAN, TEST);                                                                  |

| • Order: NORMAL < SCAN < TEST                                                                       |

| • Default initialization of signals to the 'LEFT value.                                             |

| (Attribute of a type or object, e.g. MODE'LEFT, MODE'RIGHT)                                         |

| © ECEMA 2000 Sequential constructs 2.9                                                              |

| Integer types                                                                      |    |  |  |  |

|------------------------------------------------------------------------------------|----|--|--|--|

| Examples                                                                           |    |  |  |  |

| type byte is range 0 to 255; synthesized to 8 bits                                 |    |  |  |  |

| type other is range -6 to 7; synthesized to 4bits: 2's-complement bit vector       |    |  |  |  |

| type WIDTH is range 31 downto 0;                                                   |    |  |  |  |

| type reverse is range WIDTH'LOW to WIDTH'HIGH;                                     |    |  |  |  |

| subtype AT_WIDTH is WIDTH range 15 downto 0;                                       |    |  |  |  |

| Each bound must be a locally static expression of some integer type                |    |  |  |  |

| Predefined integer types                                                           |    |  |  |  |

| The only one is the type INTEGER                                                   |    |  |  |  |

| • The range is implementation dependent                                            |    |  |  |  |

| • guaranteed to include the range: -2147483647 to + 2147483647(2**31+1 to 2**31-1) |    |  |  |  |

| • The range may be determined from attributes                                      |    |  |  |  |

| INTEGER'LOW, INTEGER'HIGH                                                          |    |  |  |  |

| © ECEMA 2000 Sequential constructs 2.                                              | 11 |  |  |  |

|              | Physical                                                                                                       | types      |      |

|--------------|----------------------------------------------------------------------------------------------------------------|------------|------|

|              | ge STANDARD<br>nclude the range -2**31<br>n of delays must be of t<br>FPGA Synthesis<br>e -1E18 <b>to</b> 1E18 |            |      |

| © ECEMA 2000 | Sequential                                                                                                     | constructs | 2.12 |

| Floating point types                                                                                                                                                                                                                                                                                         |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>Approximate real numbers</li> <li>A floating point is defined by a range constraint</li> <li>Each bound must be a locally static expression</li> <li>Each bound must be of some floating point type</li> <li>Not supported in FPGA Synthesis</li> </ul>                                             |      |

| <i>Examples</i><br><b>type</b> coord_x_type <b>is range</b> 0.0 <b>to</b> 100.0<br><b>subtype</b> One_interval <b>is</b> coord_x_type <b>range</b> 0.0 <b>to</b> 1.0;                                                                                                                                        |      |

| <ul> <li>Predefined floating point types</li> <li>REAL is the only predefined type</li> <li>Appears in package STANDARD</li> <li>Guaranteed to include the range -1E38 to +1E38</li> <li>Defined with an ascending range</li> <li>The range may be determined from attributes REAL'LOW, REAL'HIGH</li> </ul> |      |

| © ECEMA 2000 Sequential constructs                                                                                                                                                                                                                                                                           | 2.13 |

|                                  | Array types                                            |      |

|----------------------------------|--------------------------------------------------------|------|

| Composite types are:             | array types and record types                           |      |

| An array type definiti           | on may be either:                                      |      |

| <ul> <li>constrained</li> </ul>  |                                                        |      |

| <ul> <li>unconstraine</li> </ul> | d                                                      |      |

| constrained array defi           | nition                                                 |      |

| array (discrete r                | ange {, discrete range})                               |      |

| of element subty                 | pe indication                                          |      |

| unconstrained array d            | efinition                                              |      |

| array (subtype n                 | aame <b>range</b> <> {, subtype name <b>range</b> <>}) |      |

| of element subty                 | pe indication                                          |      |

|                                  |                                                        |      |

| ECEMA 2000                       | Sequential constructs                                  | 2.14 |

| Array types (cont'd)                                                                                                                                                                                                                                   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Predefined array types<br>subtype POSITIVE is INTEGER range 1 to INTEGER'HIGH<br>type STRING is array (POSITIVE range <>>) of CHARACTER;<br>subtype NATURAL is INTEGER range 0 to INTEGER'HIGH<br>type BIT_VECTOR is array (NATURAL range <>>) of BIT; |      |

| Examples<br>type mu_word is array (48 downto 0) of BIT;<br>type Memory is array (NATURAL range <>) of mu_word;                                                                                                                                         |      |

| Possible declarations in a sequential part (in the body of a process for example) <b>variable</b> ROM : Memory (0 <b>to</b> 2**N-1); <b>variable</b> ScanChain : BIT_VECTOR (0 <b>to</b> N*L);                                                         |      |

| Possible declaration in a concurrent part (in an architecture for example) <b>signal</b> mu_pc : mu_word;                                                                                                                                              |      |

| © ECEMA 2000 Sequential constructs                                                                                                                                                                                                                     | 2.15 |

|              | <b>Record types</b>        |  |

|--------------|----------------------------|--|

| Examples     |                            |  |

| type DATE is |                            |  |

| record       |                            |  |

| YEAR: P      | OSITIVE range 1 to 3000;   |  |

| MONTH:       | STRING(0 to 8);            |  |

| DAY: PO      | SITIVE range 1 to 31;      |  |

| end record;  |                            |  |

| type VERSIO  | N is                       |  |

| record       |                            |  |

| NUMBEI       | R: REAL range 0.0 to 30.0; |  |

| CREATE       | D: DATE;                   |  |

| MODIFIE      | ED: DATE;                  |  |

| end record;  |                            |  |

|              |                            |  |

|              |                            |  |

|                               | Constant declaration                                       |      |

|-------------------------------|------------------------------------------------------------|------|

| constant identifier {,        | identifier} : <b>subtype</b> indication [:= expression]    |      |

| The value of a constant       | nt cannot be modified after the declaration is elaborated. |      |

| Examples:                     |                                                            |      |

| constant normal_wei           | ght :weight := 70 kg;                                      |      |

| constant cycle : TIM          | E := 1 us;                                                 |      |

| <b>constant</b> e : real := 2 | .71828 ;                                                   |      |

| type vect_n is array          | (Positive <b>range</b> <>) <b>of</b> NATURAL;              |      |

| constant Five_Ones :          | $vect_n := (1, 1, 1, 1, 1);$                               |      |

|                               | The range of Five_Ones is 5 due to the assignment.         |      |

| Constants of type recor       | d are not supported for synthesis                          |      |

| (the initialization of red    | cords is not supported).                                   |      |

| © ECEMA 2000                  | Sequential constructs                                      | 2.18 |

| Sign                                                                                                                                                         | al declaration                                                                                                 |      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|--|--|

| signal identifier {, identifier} : su                                                                                                                        | btype indication [ bus   register] [:= expression]                                                             |      |  |  |

| • A signal is an object with a past hi                                                                                                                       | istory of values.                                                                                              |      |  |  |

| • It may have one (or many) drivers                                                                                                                          | , each with a current value                                                                                    |      |  |  |

| and projected future values.                                                                                                                                 |                                                                                                                |      |  |  |

| • The expression (if present) specifies the initial value of the signal at simulation time 0. The expression is evaluated at each elaboration of the signal. |                                                                                                                |      |  |  |

| • The default initial value for a signal of a scalar type T is T'left.                                                                                       |                                                                                                                |      |  |  |

| • Can be declared in concurrent des                                                                                                                          | criptions only.                                                                                                |      |  |  |

| <i>Examples</i><br>signals with single drivers<br>signal Clk1, Clk2 : time;<br>signal vector_5 : bit_vector (1 to 5);<br>signal index : integer := -127;     | Signals can be given default (initial) values.<br>However, these initial values are not used for<br>synthesis. |      |  |  |

| © ECEMA 2000 Seq                                                                                                                                             | juential constructs                                                                                            | 2.20 |  |  |

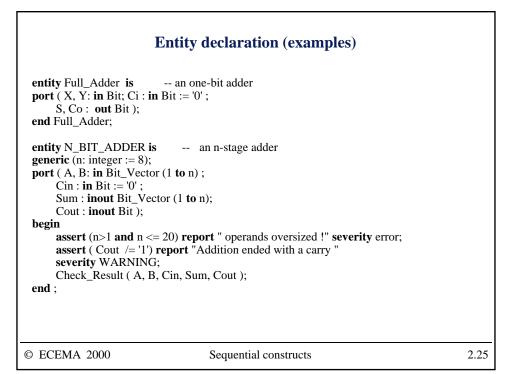

| Entity declaration                                                                                                                                       |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| entity identifier is                                                                                                                                     |  |  |  |  |  |

| entity header                                                                                                                                            |  |  |  |  |  |

| [generic ( interface constant declaration {; interface constant declaration});]                                                                          |  |  |  |  |  |

| [ <b>port</b> ( interface signal declaration {; interface signal declaration});]                                                                         |  |  |  |  |  |

| entity declarative part                                                                                                                                  |  |  |  |  |  |

| subprogram declaration, subprogram body, type and subtype declaration, constant and signal declaration, use clause, but <i>no variable declaration</i> . |  |  |  |  |  |

| All the declarations are visible throughout any architecture of the entity                                                                               |  |  |  |  |  |

| What is declared in an architecture is not visible to another architecture of the same entity.                                                           |  |  |  |  |  |

| [ begin                                                                                                                                                  |  |  |  |  |  |

| concurrent assertion statement                                                                                                                           |  |  |  |  |  |

| passive concurrent procedure call                                                                                                                        |  |  |  |  |  |

| passive process statement                                                                                                                                |  |  |  |  |  |

| ]                                                                                                                                                        |  |  |  |  |  |

| end [entity simple name];                                                                                                                                |  |  |  |  |  |

| © ECEMA 2000 Sequential constructs 2.21                                                                                                                  |  |  |  |  |  |

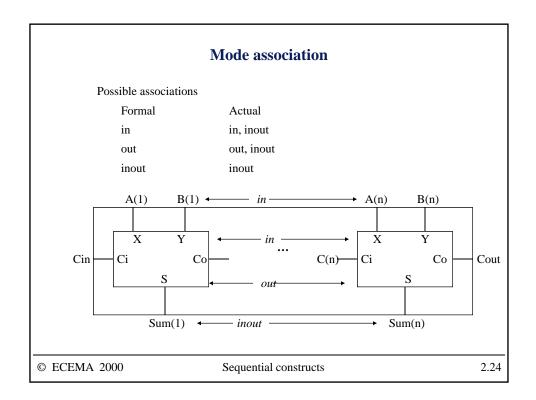

| Entity header                                                                                                             |      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| The entity header declares objects used for communication between a design entity and its environment                     |      |  |  |  |

| <i>Generics</i> allow static information to be communicated to a block from its environment. They may be used to specify: |      |  |  |  |

| • Number of inputs to a component.                                                                                        |      |  |  |  |

| • Number of subcomponents within a block.                                                                                 |      |  |  |  |

| Timing characteristics.                                                                                                   |      |  |  |  |

| • Physical characteristics of a design: temperature, capacitance, etc.                                                    |      |  |  |  |

| <i>Ports</i> provide channels for communication between an entity (or a block in general) with its environment.           |      |  |  |  |

| [signal] identifier{, identifier}:[mode] subtype indication [bus] [:= expression]                                         |      |  |  |  |

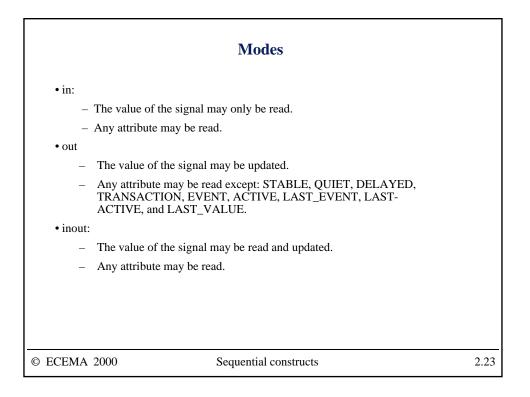

| • Modes: in (default mode), out, inout, buffer, linkage                                                                   |      |  |  |  |

| • Only signals can be in entity ports (no variables, files or access types).                                              |      |  |  |  |

| • The expression defines the default value of the signal.                                                                 |      |  |  |  |

| © ECEMA 2000 Sequential constructs                                                                                        | 2.22 |  |  |  |

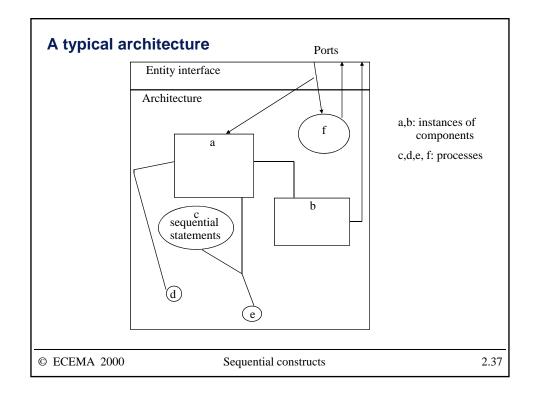

| Architectures                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| • A design entity has a unique interface ( entity decalaration), and one or more architectures.                                                                                                                                                                       |  |  |  |  |  |

| • An architecture body defines the body of the design entity.                                                                                                                                                                                                         |  |  |  |  |  |

| • It specifies the relationship between the input and the outputs                                                                                                                                                                                                     |  |  |  |  |  |

| of the design entity.                                                                                                                                                                                                                                                 |  |  |  |  |  |

| <ul> <li>architecture identifier of entity name is</li> <li>architecture declarative part</li> <li>subprogram declaration, subprogram body, type and subtype declaration, constant and signal declaration, use clause, but <i>no variable declaration</i>.</li> </ul> |  |  |  |  |  |

| What is declared in an architecture is not visible to another architecture of the same entity.                                                                                                                                                                        |  |  |  |  |  |

| begin                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| architecture statement part {concurrent statements}                                                                                                                                                                                                                   |  |  |  |  |  |

| end [architecture simple name];                                                                                                                                                                                                                                       |  |  |  |  |  |

| © ECEMA 2000 Sequential constructs 2.26                                                                                                                                                                                                                               |  |  |  |  |  |

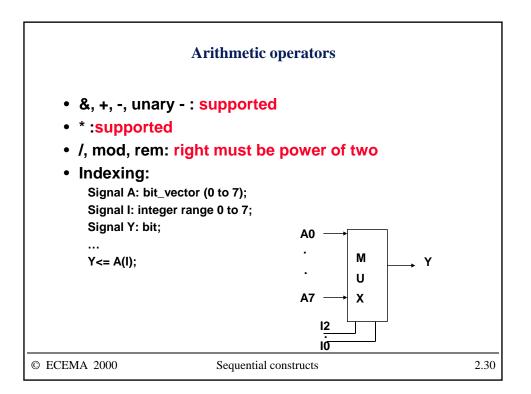

| Expressions  |                                                                |      |  |  |  |

|--------------|----------------------------------------------------------------|------|--|--|--|

|              | Operators                                                      |      |  |  |  |

|              | Classes of operators listed in order of increasing precedence. |      |  |  |  |

|              | Logical: and or nand nor xor                                   |      |  |  |  |

|              | relational = /= < <= > >=                                      |      |  |  |  |

|              | addition + - &                                                 |      |  |  |  |

|              | signs + -                                                      |      |  |  |  |

|              | multiplication * / mod rem                                     |      |  |  |  |

|              | miscellaneous ** abs not                                       |      |  |  |  |

|              | Operands                                                       |      |  |  |  |

|              | Literals                                                       |      |  |  |  |

|              | Aggregates                                                     |      |  |  |  |

|              | Qualified expressions                                          |      |  |  |  |

|              | Type conversions                                               |      |  |  |  |

|              |                                                                |      |  |  |  |

| © ECEMA 2000 | Sequential constructs                                          | 2.27 |  |  |  |

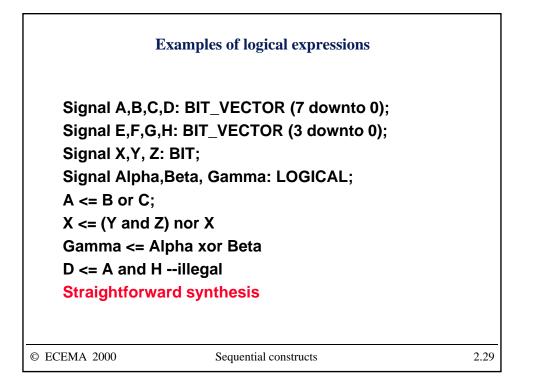

| Operators                                                                                    |

|----------------------------------------------------------------------------------------------|

| Logical operators                                                                            |

| Operands:                                                                                    |

| – BIT or BOOLEAN                                                                             |

| - One dimensional arrays which have elements of type BIT or BOOLEAN                          |

| - The arrays must have the same length.                                                      |

| Relational operators                                                                         |

| The result is BOOLEAN.                                                                       |

| For = and /= operators the operands may be of any type.                                      |

| For < , <= , > , >= operators the operands may be of any scalar type or discrete array type. |

| Addition operators:                                                                          |

| +,-: numeric types                                                                           |

| &: concatenation between 2 arrays of the same type or an arrays and an element.              |

| © ECEMA 2000 Sequential constructs 2.2                                                       |

|         | Qualified expressions                                                                                      |     |

|---------|------------------------------------------------------------------------------------------------------------|-----|

|         | <ul> <li>type mark'(expression)</li> </ul>                                                                 |     |

|         | <ul> <li>type mark'aggregate</li> </ul>                                                                    |     |

| •       | A qualified expression is used to explicitly state the type (or subtype) of an expression or an aggregate. |     |

| •       | The value of the qualified expression is the value of the operand.                                         |     |

| •       | The evaluation checks that the value of the operand belongs to the specified subtype.                      |     |

| •       | The operand must have the same type as the base type of the type mark.                                     |     |

| •       | Examples:                                                                                                  |     |

|         | POSITIVE '(34*N +M) N and M must be integers                                                               |     |

|         | STRING'("Success")                                                                                         |     |

| •       | Useful for alleviating ambiguity, when operators or subprograms are overloaded                             |     |

|         |                                                                                                            |     |

| ) ECEMA | 2000 Sequential constructs                                                                                 | 2.3 |

| Examples of type conversion                 |                                  |      |  |  |

|---------------------------------------------|----------------------------------|------|--|--|

| INTEGER (3.1459)                            | value 3                          |      |  |  |

| INTEGER (3.5)                               | implementation dependent 3 or 4  |      |  |  |

| INTEGER (3.6)                               | value 4.                         |      |  |  |

|                                             |                                  |      |  |  |

| type table is array(positive r              | range 1 to 8) of bit;            |      |  |  |

| <b>type</b> rev_table <b>is array</b> ( pos | itive range 8 downto 1) of bit;  |      |  |  |

| variable tabinc: table;                     |                                  |      |  |  |

| <pre>variable tabdec: rev_table;</pre>      |                                  |      |  |  |

|                                             |                                  |      |  |  |

| tabinc <- X"0F";                            | tabinc (1 to 8) -"0F"            |      |  |  |

| tabdec <= rev_table(table)                  | inc); tabdec (8 downto 1) = "0F" |      |  |  |

|                                             |                                  |      |  |  |

|                                             |                                  |      |  |  |

|                                             |                                  |      |  |  |

| © ECEMA 2000                                | Sequential constructs            | 2.35 |  |  |

| SR La<br>(Example of variable an                                                                                                                                                                    |                                          |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|

| <pre>entity SR_Latch is port ( S,R: in Bit; Q, QB: out Bit ); begin     assert (S=0 or R=0) report "S = R end SR_Latch;</pre>                                                                       | = '1' " <b>severity</b> error;           |     |

| architecture behave of SR_Latch is<br>begin<br>process (S, R)<br>variable state: Bit;<br>begin<br>If S /= R then<br>state := S;<br>end if;<br>Q <= state after 2 ns;<br>OR <= not state after 2 ns; | variable assignment<br>signal assignment |     |

| QB <= not state after 2 ns;<br>end process;<br>end behave ;<br>© ECEMA 2000 Sequential                                                                                                              | constructs                               | 2.3 |

| If statement (general)                                                                                                                                                                                                                                                                           |                                       |      |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|--|--|

| <pre> Number of ones in the binar<br/> Even parity of X.<br/>parity := 0;<br/>if X = 0 then<br/>nb_of_ones := 0;<br/>elsif X=7 then<br/>nb_of_ones := 3;<br/>parity := 1;<br/>elsif X=1 or X=2 or X=4 then<br/>nb_of_ones := 1;<br/>parity := 1;<br/>else<br/>nb_of_ones := 2;<br/>end if;</pre> | y representation of X of range 0 to 7 | 7.   |  |  |

| © ECEMA 2000                                                                                                                                                                                                                                                                                     | Sequential constructs                 | 2.40 |  |  |

|                       |       | Case statement                              |      |

|-----------------------|-------|---------------------------------------------|------|

| Number of ones in     | n the | binary representation of X of range 0 to 7. |      |

| Even parity of X.     |       |                                             |      |

| parity $:= 0;$        |       |                                             |      |

| case X is             |       |                                             |      |

| <b>when</b> 0         | =>    | nb_of_ones := 0;                            |      |

| when 7                | =>    | nb_of_ones := 3;                            |      |

|                       |       | parity := 1;                                |      |

| <b>when</b> 1   2   4 | =>    | nb_of_ones := 1;                            |      |

|                       |       | parity := 1;                                |      |

| when others           | =>    | nb_of_ones := 2;                            |      |

| end case;             |       |                                             |      |

| See also FSM modeling |       |                                             |      |

| © ECEMA 2000          |       | Sequential constructs                       | 2.41 |

| Null statement                                                           |                                                 |                    |      |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------|--------------------|------|--|--|

| The execution of a                                                       | The execution of a null statement has no effect |                    |      |  |  |

| Example: Rendez                                                          | zvous element:                                  |                    |      |  |  |

| X                                                                        | RES                                             |                    |      |  |  |

| $\begin{array}{c} 0\\ 1\\ 2\\ 3 \end{array}$                             | 0<br>no change<br>no change<br>1                |                    |      |  |  |

| Signal RES: Bit                                                          | <b>Signal</b> RES: Bit := 0; initial value      |                    |      |  |  |

| case X is<br>when 0                                                      | => RES <= '0';                                  |                    |      |  |  |

| <pre>when 3 =&gt; RES &lt;= '1'; when others =&gt; null; end case;</pre> |                                                 |                    |      |  |  |

| © ECEMA 2000                                                             | Sequ                                            | iential constructs | 2.43 |  |  |

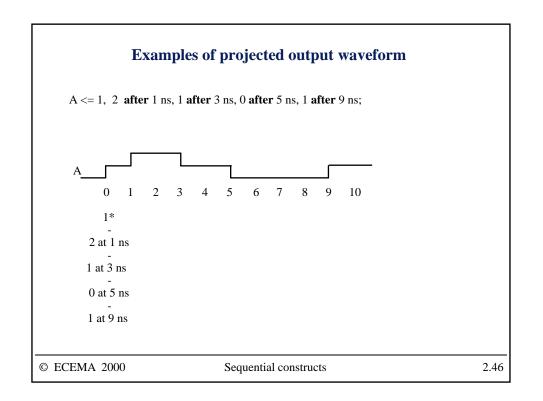

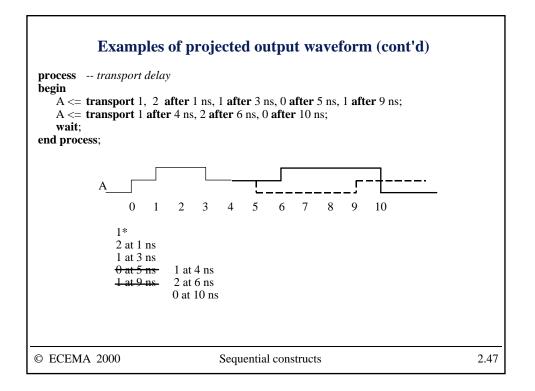

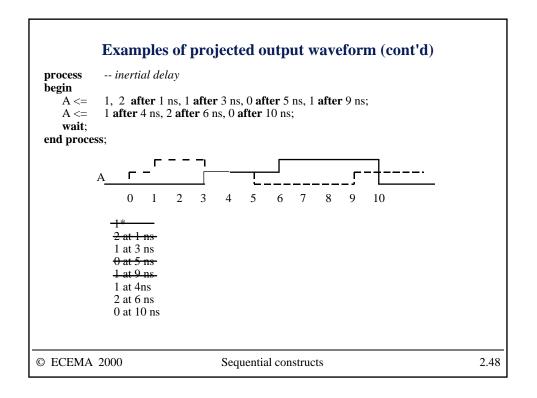

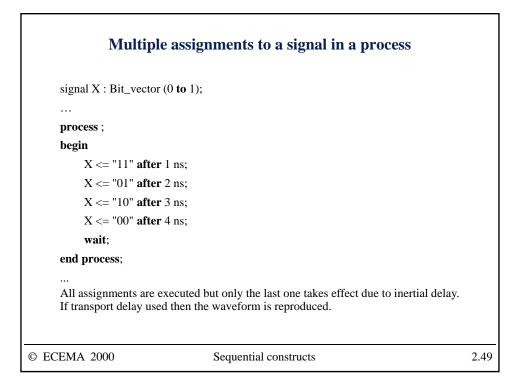

|   | Projected output waveform                                                                                                                                                                                                    |      |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | <pre>signal assignment statement target &lt;= [transport] waveform element {, waveform element}; waveform element value expression [after time expression] null [after time expression] guarded signal (see session 5)</pre> |      |

|   | If after clause missing "after 0 ns" is assumed (one delta delay).                                                                                                                                                           |      |

|   | Time expression cannot be negative.                                                                                                                                                                                          |      |

|   | null assignment turns the driver of the signal off.                                                                                                                                                                          |      |

|   |                                                                                                                                                                                                                              |      |

| © | ECEMA 2000 Sequential constructs                                                                                                                                                                                             | 2.44 |

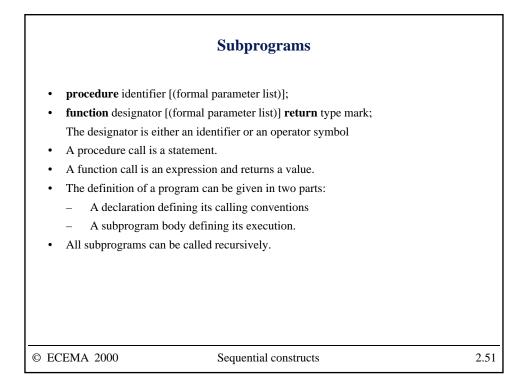

| Formal parameters                                                                                                                                                                                                                                                                                                                                                                                                 |      |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| <ul> <li>formal parameters</li> <li>may be constants, variables or signals for procedures</li> <li>may be only constants or signals for functions</li> <li>No global objects can be modified inside a function: the mode is always in.</li> <li>Mode: in, out, inout for procedures.</li> <li>variable is the default class for modes: out, inout.</li> <li>constant is the default class for mode in.</li> </ul> |      |  |  |

| <pre>syntax [constant] identifier list: [in] subtype indication [ := static expression] [signal] identifier list: [mode] subtype indication [bus] [ := static expression]] [variable]identifier list : [mode] subtype indication [:= static expression]</pre>                                                                                                                                                     |      |  |  |

| © ECEMA 2000 Sequential constructs                                                                                                                                                                                                                                                                                                                                                                                | 2.52 |  |  |

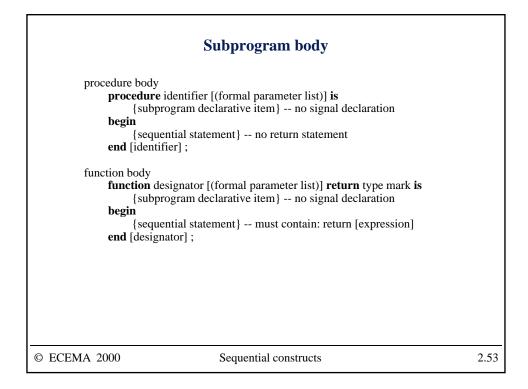

| Examples of subprograms             |                                                                                          |      |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------|------|--|--|

| function W_AND ( INI                | PUT : BIT_VECTOR ) return BIT is                                                         |      |  |  |

| variable RESULT : BI                | $\Gamma := '1';$                                                                         |      |  |  |

| pragma resolu<br>wired_and<br>Begin | ution_method                                                                             |      |  |  |

|                                     | s function is ignored by RTL synthesis bu<br>to NPUT high loop for I in INPUT range loop | t    |  |  |

| if INPUT                            | ( I ) = '0' <b>then</b>                                                                  |      |  |  |

| RESU                                | ULT := '0';                                                                              |      |  |  |

| exit;                               |                                                                                          |      |  |  |

| end if;                             |                                                                                          |      |  |  |

| end loop;                           |                                                                                          |      |  |  |

| return RESULT ;                     |                                                                                          |      |  |  |

| end W_AND;                          |                                                                                          |      |  |  |

| © ECEMA 2000                        | Sequential constructs                                                                    | 2.54 |  |  |

|      | Signal parameters                                                                                                                                                                                                                            |      |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

|      | During the execution of a subprogram, a reference to a formal within an expression is equivalent to a reference to the associated actual signal.                                                                                             |      |  |  |

| •    | An assignment to the driver of a formal signal is equivalent to an assignment to the driver of the actual signal.                                                                                                                            |      |  |  |

|      | Attributes STABLE, QUIET, DELAYED of a formal signal parameter cannot<br>be read within a subprogram, however, EVENT, ACTIVE, LAST_EVENT, and<br>LAST_ACTIVE are available since they are functional attributes of the formal<br>parameters. |      |  |  |

| © EC | EMA 2000 Sequential constructs                                                                                                                                                                                                               | 2.55 |  |  |

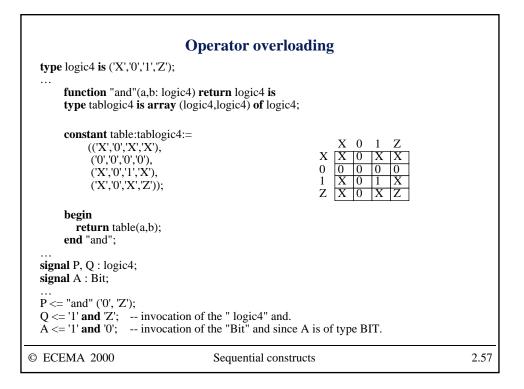

| Subprogram overloading                                                 |                                                           |      |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------|------|--|--|

| <ul> <li>A given subprogram des<br/>specifications.</li> </ul>         | ignator is overloaded if it is used in several subprogram |      |  |  |

| procedure count (C: Charac                                             | cter; S: String; NB: inout INTEGER);                      |      |  |  |

| counts the number                                                      | counts the number of occurrences of C in S.               |      |  |  |

| <pre>procedure count (B: BIT; V: BIT_vector; NB: inout INTEGER);</pre> |                                                           |      |  |  |

| counts the number                                                      | counts the number of occurrences of B in V.               |      |  |  |

| procedure check (setup:Time; signal D: Data);                          |                                                           |      |  |  |

| procedure check (hold:Time; signal D: Data);                           |                                                           |      |  |  |

|                                                                        |                                                           |      |  |  |

| count ('a', message, NB);                                              | correct implementation determined                         |      |  |  |

| count ('1', V1,NB);                                                    | from parameter types                                      |      |  |  |

| check (setup $\Rightarrow$ 10 ns, D $\Rightarrow$ DL);                 |                                                           |      |  |  |

| check (10 ns, DL);                                                     | ambiguous                                                 |      |  |  |

| See 6.13-6.14 for other examples of subprogram overloading             |                                                           |      |  |  |

|                                                                        |                                                           |      |  |  |

| © ECEMA 2000                                                           | Sequential constructs                                     | 2.56 |  |  |

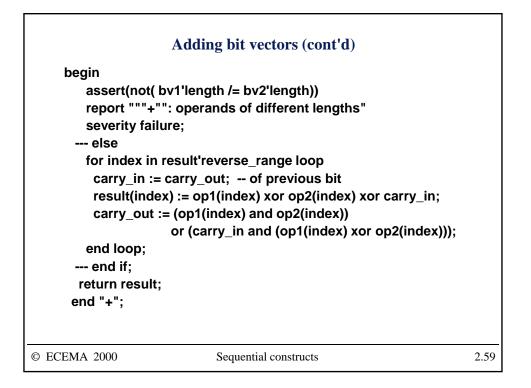

| Adding bit vectors                                                      |                       |       |

|-------------------------------------------------------------------------|-----------------------|-------|

| <br>function "+" ( bv1, b<br>alias op1 : bit_vec<br>alias op2 : bit_vec |                       | or is |

| © ECEMA 2000                                                            | Sequential constructs | 2.58  |