### **VHDL Design Flow**

### **BEHAVIORAL AND LOGIC SYNTHESIS**

El Mostapha Aboulhamid Dépt. IRO, Université de Montréal CP 6128, Succ. Centre-Ville Montréal, Qc. H3C 3J7

Phone: 514-343-6822 FAX: 514-343-5834 aboulham@iro.umontreal.ca

*Acknowledgment*: François Boyer (boyerf@iro.umontreal.ca) had a major contribution in the development of the labs contents.

VHDL Design Flow 1 General Design Flow 1 Top-down design 2 Description paradigms and abstraction levels 3 Description paradigms and abstraction levels (cont'd) 4 Data Flow Descriptions 5 Control Oriented Descriptions 6 Behavioral Descriptions 7 Behavioral Synthesis (input) 8 Scheduling 9 Allocation 10 Design validation 11 Simulation and verification 12 RTL and behavioral design 13 VHDL Synthesizable Subset 14 VHDL Synthesizable Subset (cont'd) 15 VHDL Synthesizable Subset (cont'd) 16 Special attributes 17 Main Features of Behavioral Synthesis 18 Main Features of Behavioral Synthesis (cont'd) 19 RTL Descriptions 20 Scheduling and allocation illustration 21 Behavioral Compiler Design Flow 22 Steps of the BC Design Flow 23 References 24

#### EMA1997

Design Flow Example 1 VHDL code 2 Main loop after elaboration 4 BEHAVIORAL COMPILER 1 **Objectives 2** Design flow 3 Inputs 4 Processing steps 5 Processing steps (cont'd) 6 Processing steps (cont'd) 7 BC internals Control-dataflow graph 8 CDFG 9 CDFG nodes 10 Chaining, multicycling, and pipelining 11 Chaining, multicycling, and pipelining (Illustration) 12 CDFG edges 13 Speculative execution 14 Templates 15 Scheduling 16 Scheduling (cont'd) 17 Scheduling (cont'd) 18 Allocation 19 Allocation (cont'd) 20 Allocation criteria 21 Netlisting 22 Control FSM 23 States and csteps 24 BC constraints on loops 25

-1 of 8

Invoking the scheduler 26 HDL descriptions and semantics 1 Objectives 2 Pre-synthesis model 3 The design 4 The design (cont'd) 5 Behavioral processes 6 Behavioral processes (cont'd) 7 Clock and Reset 8 Synchronous resets 9 Synchronous resets (cont'd) 10 Asynchronous resets 11 I/O Operations 12 I/O Operations 13 I/O Operations (cont'd) 14 Flow of Control 15 Fixed bound FOR loops 16 General loops 17 Pipelined loops 18 Pipelined loops 19 Pipelined loops and Fixed I/O mode 20 Other I/O modes 21 Memory inference 22 Memory code 23 Memory timing 24 Memory timing (cont'd) 25 Other memory considerations 26 Synthetic components 27 DesignWare developer 28

#### EMA1997

Preserved functions 29 Pipelined components 30 I/O modes 1 I/O modes 2 I/O modes (cont'd) 3 Cycle-Fixed Mode 4 Cycle-Fixed Mode (Test bench) 5 Fixed Mode rules (Straight line code) 6 Fixed Mode rules (Loops) 7 Loops in fixed mode 8 Nested loops and FM 9 Successive loops and FM 10 Complex loop conditions 11 Superstate-Fixed Mode 12 Superstate-Fixed Mode (Implications) 13 Superstate Rules (continuing superstate) 14 Superstate Rules (separating write orders) 15 Superstate Rules (Conditional superstate) 16 Superstate Rules (Escaping from the loop) 17 Free-Floating Mode 18 Explicit Directives and Constraints 1 Labeling

- 3 of 8

(Default naming) 2 Labeling (user naming) 3 Labeling (improved naming) 4 Scheduling Constraints 5 Scheduling Constraints (cont'd) 6 Shell Variables 7 Shell Variables (cont'd) 8 Shell Commands 9 RTL Design Methodology 1 RTL Design flow 2 RTL Design flow 3 Design refinement 4 HDL FF Code 5 HDL latch Code 6 HDL AND Code 7 MUX inference 8 MUX modeling 9 Synthesized gate-level netlist simulation 10 Netlist simulation (cont'd) 11 Simulation of commercial ASICs 12 Design for Testability 13 Design Re-use 14 Designing with DW Components 15 FPGA Synthesis 16 Links to layout 17 DC and DA environments 18 DC and DA environments

#### EMA1997

- 5 of 8

(cont'd) 19 Target, Link, and Symbol Libraries 20 Libraries generation 21 VHDL RTL SEMANTICS 1 Types, signals and variables 2 Buffer mode modeling 3 STD\_LOGIC 4 Arithmetic 5 Unwanted latches 6 Asynchronous reset 7 Synchronous reset 8 VHDL specifics 9 VHDL specifics (cont'd) 10 Finite state machines 11 State encoding 12 HDL description of a state machine 13 Recommended style 14 Enumerated types and encoding 15 General description of FSM 16 Guidelines for FSM coding 17 fail-safe behavior 18 Memories 19 Memory behavior 20 Barrel shifter 21 Multi-bit register 22 Methodology for RTL synthesis 1 Objectives 2 Synthesis constraints 3 Design rule constraints 4

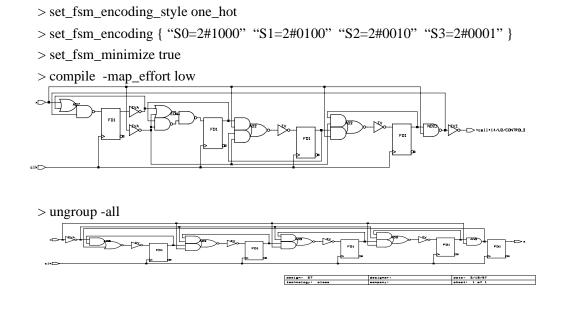

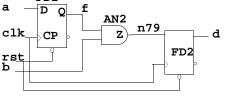

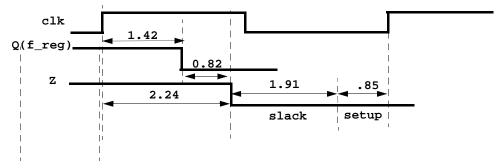

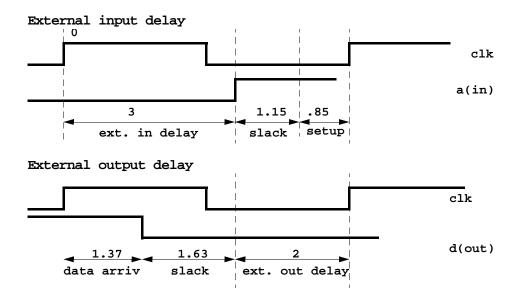

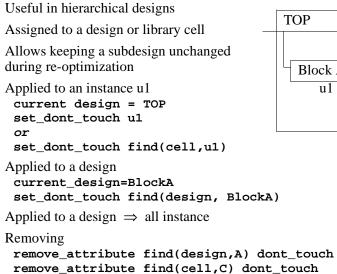

DRC 5 Related commands 6 Optimization constraints 7 Cost functions 8 Clock specification 9 Timing reports 10 Design after read 11 VHDL after READ 12 Basic Sequential Element 14 After compilation to lsi\_10k; 16 Reports 17 Set\_dont\_touch 22 Flattening 23 Structuring 24 Grouping and using 25 Characterization 26 Guidelines 27 Guidelines (cont'd) 28 Guidelines (cont'd) 29 Finite State Machines 1 Extracting FSMs 2 Coding FSMs in VHDL 6 VHDL Design Flow LAB 1 1 Lab1 VHDL code 5 LAB 2 7 VHDL code lab 2 9 LAB 3 11 VHDL code LAB 3 13 LAB 4 15

EMA1997

- 7 of 8

VHDL code LAB 4 18 LAB 5 21 LAB 5 VHDL code 25 Protocol case study 28 29 LAB 6 33 LAB 6 VHDL CODE 35

### **I.** General Design Flow

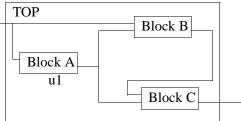

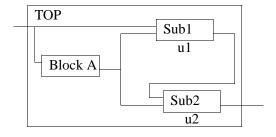

### **Top-down design**

- +: Rough outlines explored at the highest possible level

- +: Fine-grained optimization at lower levels

- +: Wider variety of design can be explored at the higher levels Functionality partitioned into blocks and processes Blocks can be mapped to software or hardware

- +: At lower levels exploration limited to: Area Speed Testability Power consumption

- -: Iteration between levels may be inevitable

### Description paradigms and abstraction levels

#### **Data flow**

Input data as stream of samples Stream oriented operations Tools: graphical or dataflow oriented languages (Silage)

### **Control oriented**

Emphasis on states and transitions

Ex: Protocol descriptions Graphical or languages or both: SDL

#### FIFOs

High level synchronization mechanisms

Non-determinism

Output can be sent either to RTL synth. or behav. synthesis Depending on states corresponding to circuit states or not

EMA1997

General Design Flow

I - 3 of 24

# Description paradigms and abstraction levels (cont'd)

### Behavioral

Language based Offers scheduling and allocation Front-end to RTL synthesis

### RTL

Language or graphical Hierarchy Finer optimizations Technology independent

### Gate

### **Data Flow Descriptions**

Data represented as streams of samples

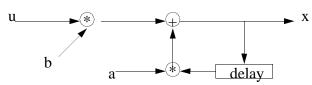

$x = axz^{-1} + bu$ : Two synchronized streams produce a third stream

Abstraction enables very fast simulation

Synthesis

Transform a stream oriented description into a time-oriented description  $x_k = ax_{k-1} + bu_k$

Synthesis at either RTL or behavioral level

Why considered high level? Stream through a time-varying channel Statistical analysis, work load ...

EMA1997

General Design Flow

I - 5 of 24

### **Control Oriented Descriptions**

#### **Emphasis on states and transitions**

#### Input: graphical or textual or both

#### May be hierarchical

#### Synthesis

Mapping to a HDL text

RTL or behavioral synthesis depending on the level of abstraction

#### Differences with data flow representation

- DF: Collection of streams where each element of a stream is processed in a similar way

- ST: Data and treatment less regular Different behaviors in different states

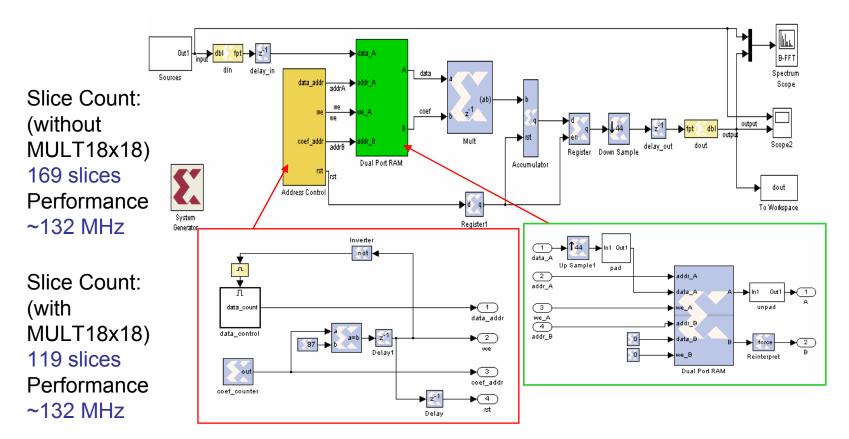

# Lab 7: Building a MAC FIR Filter Solution

Speed files: PRODUCTION v1.93

### **Behavioral Descriptions**

### Backend to Dataflow or Control oriented descriptions

### **General purpose**

### Language based: VHDL, Verilog, C, ISP, Pascal, etc.

#### HDL advantages:

Standardized Simulatable Readable interchange formats

### VHDL and Verilog

- + High quality simulators

- + Existing RTL and logic synthesis tools

- + Large customer base of designers

- Closed tools (academic point of view)

EMA1997

General Design Flow

I - 7 of 24

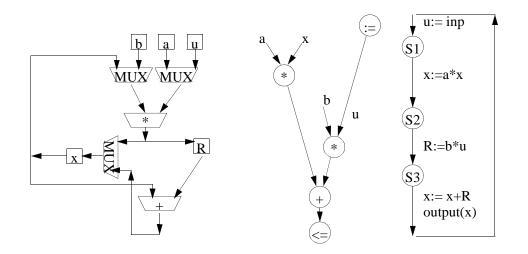

# Behavioral Synthesis (input)

#### Input = one process

```

process

variable x, u: integer := 0;

begin

u := inp;

x:= a*x + b*u;

outp <= x;

wait until clock'event and clock=1;

end;</pre>

```

Clock edges may be added during behavioral synthesis If many process: each process scheduled independently Mixed descriptions allowed: glue logic, RTL processes, behav. processes

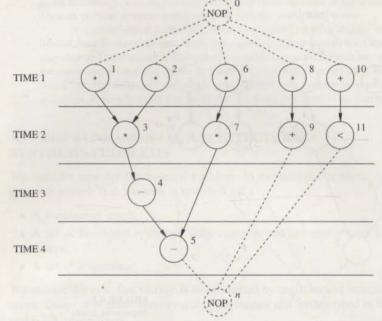

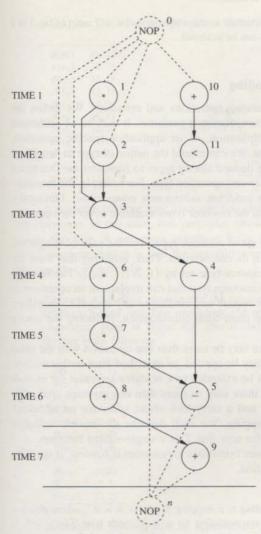

### Scheduling

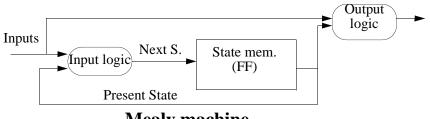

Input= process ⇒ Output= FSM + datapath Operations assigned to states User Responsibility in RTL synthesis States are part of an FSM Additional states if allowed by the user States = actual machine states Transitions correspond to machine's clock edge Machine clock (10 Mhz) may be much faster than the sample clock (50KHz) In RTL and behavioral machine clock considered In Data Stream sample clock is considered

EMA1997

General Design Flow

I - 9 of 24

### Allocation

#### **Operations assigned to functional hardware**

#### Data values assigned to storage elements

Optimization algorithm based on variables lifetime

#### Broader possibilities at behavioral level / RTL

Trade-off area/latency Register area/combinational-interconnect area

### **Design validation**

EMA1997

General Design Flow

I - 11 of 24

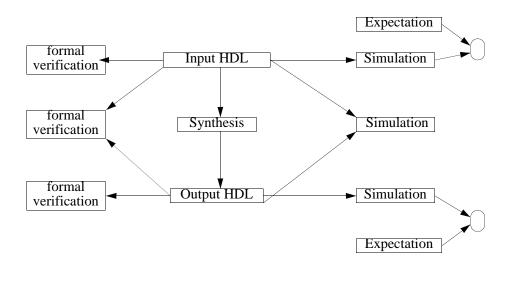

### Simulation and verification

#### Simulation

Test the response of the design under a selected set of inputs

Never exhaustive

Generation and application very time-consuming

Coverage has to be defined

Present way of validating designs

#### **Formal verification**

Test mathematical properties

Proof "equality" of two designs Equality of boolean expressions Bissimultaion in process algebra (CCS)

Not yet the main stream

Strict methodology for specification

Alleviates simulation limitations

### **RTL** and behavioral design

#### **Behavioral synthesis**

A gap between domain specific tools and RTL synthesis tools

A higher level of abstraction for the designer to logic synthesis

#### HDL design flow

Initial model in C or C++ or "simulation VHDL" Define and test the functional aspects of the design:

•bit widths, operation ordering, rounding strategies in a filter design

•number of operations necessary to unpack a field and store a packet in a ATM packet router

Timing, States and other properties at an abstract level: unlimited queues.

Initial model translated into an HDL model

Accurate and natural modeling of concurrency and time Simulation of the interaction between modules Refinement of interfaces

#### Synthesis

requires the use of a subset of the HDL

EMA1997

General Design Flow

I - 13 of 24

### VHDL Synthesizable Subset

#### **Fully supported**

Arith, log., relational *operators Entity declarations; Architecture bodies, Arrays Attributes*: RIGHT, LEFT,HIGH, LOW, BASE , RANGE, LENGTH Component declarations and instantiations Concurrent procedure calls; concurrent signal assignments; constant declarations Enumerated, integer types; If, case, loop statements Next, return statements Subprograms, declarations, bodies; subprog. and operator overloading Qualified and static expressions Type conversions Package declarations and bodies

### VHDL Synthesizable Subset (cont'd)

### **Partially supported**

Aggregates wait and EVENT on clock edge Exit only from local or reset loop Transport delay in pipeline Limited resolution functions: wired and, or, three-state No waveforms

#### Ignored

Access and file type Aliases ; Assertions Floating point, Physical types

EMA1997

General Design Flow

I - 15 of 24

### VHDL Synthesizable Subset (cont'd)

#### Unsupported

Allocators Disconnection TEXTIO Attributes: POS, VAL, SUCC, PRED, LEFTOF, RIGHTOF DELAYED, TRANSACTION RIGHT(N), LEFT(N). RANGE(N), REVERSE\_RANGE(N), HIGN(N), LOW(N) ACTIVE, LAST\_ACTIVE, LAST\_EVENT

### **Special attributes**

ARRIVAL, FALL\_ARRIVAL, RISE\_ARRIVAL DRIVE, RISE\_DRIVE, FALL\_DRIVE LOGIC\_ONE, LOGIC\_ZERO EQUAL, OPPOSITE DONT\_TOUCH\_NETWORK LOAD DONT\_TOUCH MAX\_AREA ENUM\_ENCODING UNCONNECTED HOLD\_CHECK, SETUP\_CHECK MAX\_TRANSITION, MAX\_DELAY, MIN\_DELAY, MIN\_RISE\_DELAY, MIN\_FALL\_DELAY

EMA1997

General Design Flow

I - 17 of 24

### **Main Features of Behavioral Synthesis**

Automatic assignment of non-I/O operations to states

#### I/O scheduling is more restricted

### Automatic construction of the FSM

### **Operations mapped onto hardware taking into account different trade-offs**

Number of functional units

Latency

Exploration time

Interconnects

Unit selection (carry lookahead vs. ripple carry): may be overridden manually

# Main Features of Behavioral Synthesis (cont'd)

### Allocation of variables to registers

Optimization algorithm Based on life-time intervals

#### Easy changes

Number of states in a pipeline by changing a single constraint May result in a change in the control FSM

#### **Further steps**

Logic optimization Test insertion Retiming

EMA1997

General Design Flow

I - 19 of 24

### **RTL Descriptions**

### RTL descriptions 3 to 5 times longer than behavioral descriptions

More development time to get a good model

More errors

Less readable

### Management of next state transition by the user

### The user has to manage most of the allocation of registers

### More difficult to deal with

Conditions, pipelining, multiple cycle operations Memory and register Reads an Writes Loops boundaries subprograms

### Scheduling and allocation illustration

EMA1997

General Design Flow

I - 21 of 24

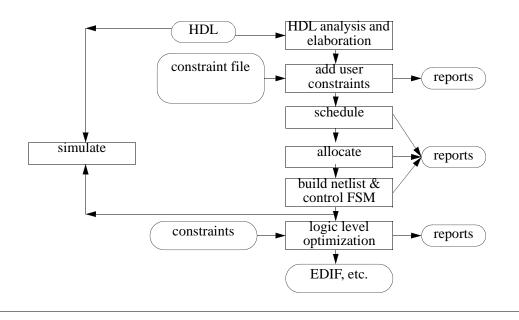

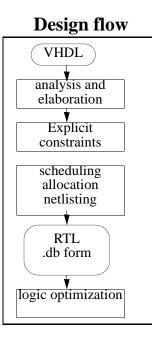

### **Behavioral Compiler Design Flow**

### Steps of the BC Design Flow

Analysis: parsing and preliminary semantics

Elaboration: different from simulation Mixed control/dataflow representation Explicit parallelism

Explicit constraints I/O operations Target technology Clock cycle

Early timing analysis (allows chaining of operations)

Scheduling

Allocation

Reports on all the previous steps

If not satisfied reiterate by changing constraints

otherwise proceed with logic synthesis

EMA1997

General Design Flow

I - 23 of 24

### References

David W. Knapp, "Behavioral Synthesis, Digital System Design Using the Synopsys behavioral Compiler," Prentice Hall PTR, 231 pages, 1996. Covers behavioral synthesis and different case studies

Pran Kurup and Taher Abbasi, "Logic Synthesis Using Synopsys," Second Edition,

Kluwer, 322 pages, 1997. Covers logic synthesis Original presentation Interesting scenarios

Giovanni De Micheli, "Synthesis and Optimization of Digital Circuits," McGraw-Hill, 579 pages, 1994. Best book on theory and algorithms for HLS

Pipelines not covered

Departs from Synopsys view of I/O

On-line Synopsys Documentation Hyperlink- documentation Complete

### **II. Design Flow Example**

### **VHDL code**

```

package types is

subtype small_int is integer range 0 to 255;

end types;

library ieee;

use ieee.std_logic_1164.all;

use work.types.all;

entity ex_bhv is

port(clk,stop: in std_logic; inport,alpha,beta: in small_int;

outport: out small_int);

end ex_bhv;

library ieee;

use ieee.std_logic_1164.all;

architecture algo of ex_bhv is

begin

process

```

```

variable a,b,u,x:small_int ;

begin

Reset_loop: loop

-- Reset tail

outport <= 0;</pre>

u:= 0; x:=0;

a:= alpha;

b:= beta;

wait until clk'event and clk='1';

if stop ='1' then exit reset_loop; end if;

main_loop: loop

-- normal mode behavior

u := inport;

x:= a*x + b*u;

outport <= x;

wait until clk'event and clk='1';

if stop ='1' then exit reset_loop; end if;

end loop main_loop;

end loop Reset_loop;

end process;

end algo;

```

Design Flow Example

II - 3 of 13

### Main loop after elaboration

```

bc_analyzer> bc_time_design

Cumulative delay starting at inport_33:

inport_33 = 0.000000

mul_{34_2} = 16.996946

add_34 = 19.182245

outport_35 = 19.182245

Cumulative delay starting at mul_34_2:

mul_{34} = 17.055845

add_34 = 19.241144

outport_35 = 19.241144

Cumulative delay starting at mul_34:

mul_{34} = 17.055845

add_34 = 19.241144

outport_{35} = 19.241144

Cumulative delay starting at outport_35:

outport_35 = 0.000000

Cumulative delay starting at add_34:

add_34 = 13.757200

outport_35 = 13.757200

Cumulative delay starting at beta_28:

beta_{28} = 0.000000

Cumulative delay starting at alpha_27:

alpha_27 = 0.000000

```

Design Flow Example

II - 5 of 13

```

bc_analyzer> create_clock -name "clk" -period 18 -waveform { "0" "9" } { "clk" }

bc_analyzer> bc_check_design

Error: Fixed IO schedule is unsatisfiable (HLS-52)

bc_analyzer> bc_check_design -io su

No errors were found.

bc analyzer> schedule -io su -eff zero

Operation schedule of process process 20:

Resource types

------

beta.....8-bit input port

loop.....loop boundaries

p0.....8-bit input port alpha

p1.....8-bit input port inport

p2.....8-bit registered output port outport

r29.....(8_8->8)-bit DW01_add

r41.....(8_8->16)-bit DW02_mult

r47.....(8_8->16)-bit DW02_mult

```

|                  |      | p<br>o<br>r<br>t | P<br>o<br>r<br>t | P<br>o<br>r<br>t | D<br>W<br>0<br>1<br>a<br>d<br>d | D<br>W<br>0<br>2<br><br>u<br>1<br>t | D<br>W<br>0<br>2<br>m<br>u<br>1<br>t  | P<br>O<br>r<br>t |

|------------------|------|------------------|------------------|------------------|---------------------------------|-------------------------------------|---------------------------------------|------------------|

| cycle            | loop | beta             | Ъ0               | p1               | r29                             | r47                                 | r41                                   | p2               |

| 0<br>1<br>2<br>3 | L0   |                  |                  | .R33.            | .0841.                          | .01150.                             | • • • • • • • • • • • • • • • • • • • |                  |

Design Flow Example

II - 7 of 13

Operation name abbreviations ------L0.....loop boundaries process\_20\_design\_loop\_begin L1.....loop boundaries process\_20\_design\_loop\_end L2.....loop boundaries process\_20\_design\_loop\_cont L3.....loop boundaries Reset\_loop/Reset\_loop\_design\_loop\_begin 14.....loop boundaries Reset\_loop/Reset\_loop\_design\_loop\_end L5.....loop boundaries Reset\_loop/Reset\_loop\_design\_loop\_cont L6.....loop boundaries Reset\_loop/main\_loop/main\_loop\_design\_loop\_begin L7.....loop boundaries Reset\_loop/main\_loop/main\_loop\_design\_loop\_end L8.....loop boundaries Reset\_loop/main\_loop/main\_loop\_design\_loop\_cont R27.....8-bit read Reset\_loop/alpha\_27 R28.....8-bit read Reset\_loop/beta\_28 R33.....8-bit read Reset\_loop/main\_loop/inport\_33 W25.....8-bit write Reset loop/outport 25 W35.....8-bit write Reset\_loop/main\_loop/outport\_35 o841.....(8\_8->8)-bit ADD\_UNS\_OP Reset\_loop/main\_loop/add\_34 oll50.....(8 8->16)-bit MULT UNS OP Reset loop/main loop/mul 34 2 oll50a.....(8\_8->16)-bit MULT\_UNS\_OP Reset\_loop/main\_loop/mul\_34

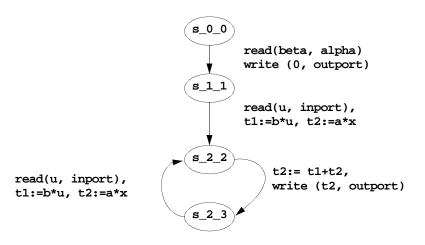

$bc\_analyzer> report\_schedule \ -abstract\_fsm> fsm\_rpt$

| ************************************** |   |       |                                                                                                                                                    |  |  |

|----------------------------------------|---|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| present next<br>state input state      |   |       | actions                                                                                                                                            |  |  |

| s_0_0                                  | - | s_1_1 | a_0: Reset_loop/beta_28 (read)<br>a_1: Reset_loop/alpha_27 (read)<br>a_4: Reset_loop/outport_25 (write)                                            |  |  |

| s_1_1                                  | - | s_2_2 | <pre>a_2: Reset_loop/main_loop/inport_33 (read) a_7: Reset_loop/main_loop/mul_34_2 (operation) a_13: Reset_loop/main_loop/mul_34 (operation)</pre> |  |  |

| s_2_2                                  | - | s_2_3 | <pre>a_3: Reset_loop/main_loop/outport_35 (write) a_22: Reset_loop/main_loop/add_34 (operation)</pre>                                              |  |  |

| s_2_3                                  | - | s_2_2 | <pre>a_2: Reset_loop/main_loop/inport_33 (read) a_7: Reset_loop/main_loop/mul_34_2 (operation) a_13: Reset_loop/main_loop/mul_34 (operation)</pre> |  |  |

EMA1997

Design Flow Example

II - 9 of 13

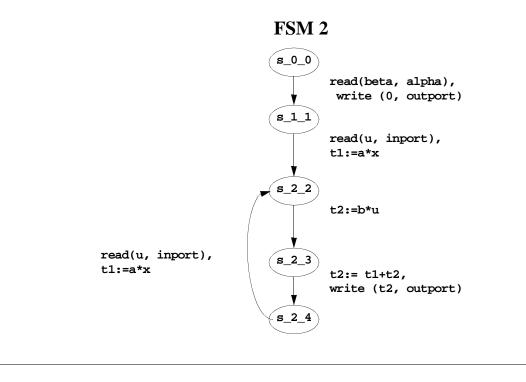

### FSM

### bc\_analyzer> remove\_design -design

bc\_analyzer> schedule -io su -eff zero -area

| i> seneuu | 10 5u                                                | CII LUIO                                                                                                         | urcu                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

|-----------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|

|           | р                                                    | р                                                                                                                | р                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                               | m                         | р                                                                                                                   |

|           | 0                                                    | 0                                                                                                                | 0                                                                                                                                                                                                        | a                                                                                                                                                                                                                                                                               | u                         | 0                                                                                                                   |

|           | r                                                    | r                                                                                                                | r                                                                                                                                                                                                        | d                                                                                                                                                                                                                                                                               | 1                         | r                                                                                                                   |

|           | t                                                    | t                                                                                                                | t                                                                                                                                                                                                        | d                                                                                                                                                                                                                                                                               | t                         | t                                                                                                                   |

| +         |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| 100b      | Deta                                                 | p0                                                                                                               | pi                                                                                                                                                                                                       | T29                                                                                                                                                                                                                                                                             | T41                       | P2                                                                                                                  |

| <br> т.3  | <br> .R28                                            | <br>. R27.                                                                                                       | <br>                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                 |                           | <br> .w25.                                                                                                          |

|           |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

|           |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

|           |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| •••••     |                                                      | ••••                                                                                                             | ••••                                                                                                                                                                                                     | ••••                                                                                                                                                                                                                                                                            | .01150                    |                                                                                                                     |

|           |                                                      |                                                                                                                  |                                                                                                                                                                                                          | .0841.                                                                                                                                                                                                                                                                          |                           | .W35.                                                                                                               |

| L8        |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| L7        |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| L5        |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| L4        | <b>.</b>                                             |                                                                                                                  | <b>.</b>                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| L2        |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

| L1        |                                                      |                                                                                                                  |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                 |                           |                                                                                                                     |

|           | loop<br>L3<br>L0<br>L6<br>L8<br>L7<br>L5<br>L4<br>L2 | p<br>o<br>r<br>t<br>loop   beta<br>.L3   .R28<br>.L0  <br>.L6.  <br>.L6.  <br>.L8.  <br>.L7.  <br>.L5.  <br>.L4. | p       p         o       o         r       r         t       t         loop       beta       p0         .L3       .R28       .R27.         .L0           .L6           .L8           .L7           .L44 | p       p       p       p         o       o       o         r       r       r         t       t       t         loop       beta       p0       p1         .L3       .R28       .R27.          .L0            .L6            .L8.            .L8.            .L5.            .L4 | p       p       p       p | p     p     p     m       o     o     o     a     u       r     r     r     d     1       t     t     t     d     t |

EMA1997

Design Flow Example

II - 11 of 13

| present next<br>state input stat |                                                                                                                                                   |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| s_0_0 - s_1_1                    | a_0: Reset_loop/beta_28 (read)<br>a_1: Reset_loop/alpha_27 (read)                                                                                 |

| s_1_1 - s_2_2                    | <pre>a_4: Reset_loop/outport_25 (write) a_2: Reset_loop/main_loop/inport_33 (read) a_10: Reset_loop/main_loop/mul_34 (operation)</pre>            |

| s_2_2 - s_2_3                    | a_7: Reset_loop/main_loop/mul_34_2 (operation)                                                                                                    |

| s_2_3 - s_2_4                    | a_3: Reset_loop/main_loop/outport_35 (write)                                                                                                      |

| s_2_4 - s_2_2                    | <pre>a_19: Reset_loop/main_loop/add_34 (operation) a_2: Reset_loop/main_loop/inport_33 (read) a_10: Reset_loop/main_loop/mul_34 (operation)</pre> |

|                                  |                                                                                                                                                   |

Design Flow Example

II - 13 of 13

### **III. BEHAVIORAL COMPILER**

A CONCEPTUAL FRAMEWORK

### Objectives

#### **BC** description

Inputs and outputs, capabilities and internal structure Provides a conceptual framework Understand error messages, the processing of the design Design good inputs to the BC

### Interfaces

BC is a collection of function embedded in a program: bc\_shell Textual Graphic interface: Design Analyzer (DA) tool

BEHAVIORAL COMPILER

III - 3 of 26

### Inputs

#### Input mechanisms

HDL text

bc\_shell command language

Pragma directives: comments embedded in the HDL text

#### HDLs

VHDL and Verilog

One or more processes + logic external to processes

BC does not process any interaction between processes

Considers a process at a time without any ordering between processes

### **Processing steps**

bc\_shell> analyze -f vhdl mydesign.vhd

#### **Elaborate Command**

bc\_shell> elaborate -s mydesign

The **s** flag: elaborate for scheduling.

Can be overridden by the attribute **rtl** attached to the process

$\Rightarrow$  mix both behavioral and RTL processes

Elaboration mode determined for each process

#### **User constraints**

Fixing a clock period and specifying the clock signal is mandatory bc\_shell> create\_clock clk -period 9

Pairs of operations can be constrained bc\_shell> set\_cycles 3 -from op1 to op2 Implementation of components may be forbidden

EMA1997

BEHAVIORAL COMPILER

III - 5 of 26

### **Processing steps (cont'd)**

#### Timing analysis

BC is a specific technology scheduler If long clock cycle operations may be chained This step is invoked manually bc\_shell > bc\_time\_design BC timing analysis is accurate: *bit\_level* instead of *lumped* timing models Report on combinational chains

### **Processing steps (cont'd)**

#### Poss. changes after report on timing

Change the clock cycle or technology if needed

Estimate required number of cycles

Guide for manual implementation selection

Indicate multicycle operations: costly in both area and timing

$\Rightarrow$  The user may decide to change the operation, the implementation or the clock cycle

#### Scheduling

Operations mapped to control steps

Non-concurrent operations may share the same multiplexed hardware

$\Rightarrow$  reduces cost while meeting performance requirements

bc\_shell> schedule -effort low

EMA1997

BEHAVIORAL COMPILER

III - 7 of 26

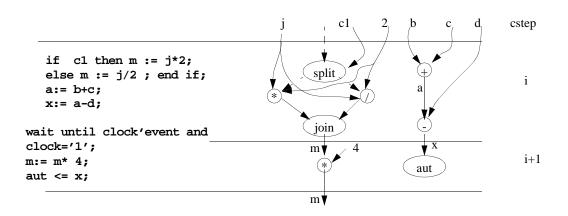

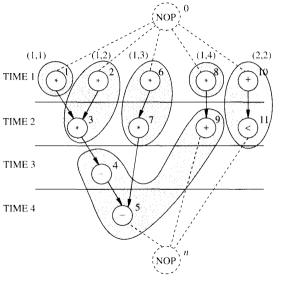

### BC internals Control-dataflow graph

### CDFG

#### CDFG

Abstract representation of the circuit behavior Without bias toward any schedule

### Terminology

+, -, \*, / belonging to cstep i are concurrent

BC (not DC) will allow "-" moved to next cstep

⇒ a dual unit add/sub can be shared

CDFG edges represent precedence

Latency: total number of csteps

EMA1997

BEHAVIORAL COMPILER

III - 9 of 26

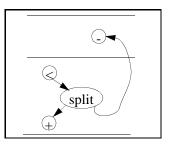

### **CDFG nodes**

#### Data

Arith/logic operations, some function calls *Synthetic* nodes share hardware, *random logic* not Patch boxes: bit and field selection, constant sources Memory R/W: memory accesses IO R/W: R/W to ports or signals

#### Conditional

split, join

### Hierarchical

loops and function calls

#### **Place holder**

#### Loop control

loop begin, loop end, loop continue, loop exit

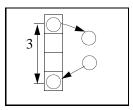

### Chaining, multicycling, and pipelining

#### **Controlling chaining**

use set\_cycles instead of bc\_shell> bc\_enable\_chaining = false

### Multicycling

Controls and muxes should be registered

If conditional, FSM should commit at cycle i-1 to stabilize registers  $\Rightarrow$  extra cstep

Forcing unicycling regardless of timing analysis, use with caution: bc\_shell> bc\_enable\_multi\_cycle = false

### Pipelining

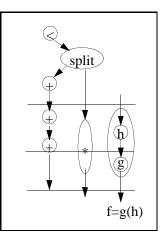

f(x) = g(h(x)): a register isolates h for g Pipelining either automatic or by implementation directives More expensive than a k-cycle operation but k times faster Multiplication and memory operations are prime candidates

EMA1997

BEHAVIORAL COMPILER

III - 11 of 26

### Chaining, multicycling, and pipelining (Illustration)

### **CDFG edges**

### Data edges

Represent values

### Precedence edges

Represent order and control

t and f of a split node

Constraints

bc\_shell> set\_min\_cycles 3 -from sub1 -to add3

EMA1997

BEHAVIORAL COMPILER

III - 13 of 26

### **Speculative execution**

Pre-computed result

stored into a register

discarded if branch not taken

Default: Turned off

search space and execution time bc\_shell> bc\_enable\_speculative\_execution

### **Templates**

Precedence and data arcs cannot express maximum allowable duration Prescheduled sub-design has to be preserved

#### Templates

Collection of operations allowed to move only as a group

Rigid timing relationship between its elements

Slots contain either place holders and/or other nodes

Notice them when impossible schedule

EMA1997

BEHAVIORAL COMPILER

III - 15 of 26

### Scheduling

#### Objective

Minimize hardware cost within user timing constraints

Ex: 2 additions on a single adder if occurring in  $\neq$  csteps or mutually exclusive

Minimize cost of registers

Lower(nb registers)= min nb of bits crossing cstep boundaries

### Algorithm

while all operations not scheduled Choose the most important unscheduled operation OP Assign OP to the most cost effective step Mark OP as scheduled

### Scheduling (cont'd)

### Criteria for selecting operations op

Ready highest implementation cost mobility

### Criteria for selecting the appropriate csetp t

op must be ready at t consumers of op are critical Clock cycle must be respected (regarding chaining) Resource and/or timing constraints Register cost

EMA1997

BEHAVIORAL COMPILER

III - 17 of 26

### Scheduling (cont'd)

### **Additional complexity**

- Conditional

- Loops

Pipelining

Memory operations

### To avoid excessive iterations use achievable constraints

Iteration are very fast compared to logic level

### BC schedules bottom up

Innermost loops and functions calls first Inline each completed level Inlined loops encapsulated in templates Inconsistencies may appear at higher levels due to templates

```

x(0) = x; y(0) = y; y'(0) = u

y'' + 3xy' + 3y = 0

eqdiff {

lire (x, y, u, dx, a)

répéter {

x1 = x + dx;

u1 = u - (3 * x * u * dx) - (3 * y * dx);

y1 = y + u * dx;

c = x1 > a;

x = x1; u = u1 ; y = y1;

}

jusqu'à (c);

écrire (y);

}

```

### Allocation

Operation should be mapped on particular hardware resources The number of resources is supposed given from the scheduling step Unit selection and mapping affects both speed and cost

```

Unallocated = operations & values

While unallocated

choose U

if not( free(R, time(U)) & Impl(R,U))

then add new resource R

assign(U, best (R))

mark U allocated

```

EMA1997

BEHAVIORAL COMPILER

III - 19 of 26

### Allocation (cont'd)

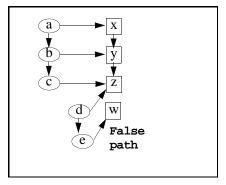

Avoid false path otherwise logic synthesis will have hard time (a, b, c), (d, e) chained operations Diff. csteps

### **Allocation criteria**

#### Cost

Allocate the most expensive operations first

#### **Critical path**

Operations and operands affecting the clock cycle first

#### Interconnect

Cluster operations and operands

$\Rightarrow$  Minimize interconnects

$\Rightarrow$  Avoid false paths

> set\_common\_resource op1 op2 op3 -mincount 2

EMA1997

BEHAVIORAL COMPILER

III - 21 of 26

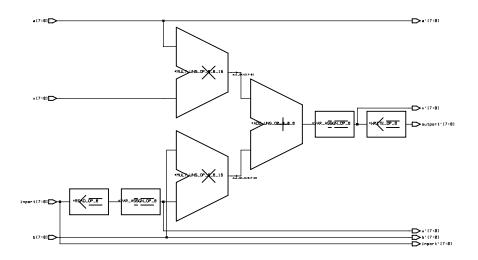

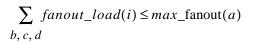

### Netlisting

#### Output of BC goes to logic synthesis

Random logic required by the user is instantiated Register, operators, memories are instantiated according to the allocation step MUXes, nets, connectivity hardware are constructed to connect the datapath Whole design connected to signals and ports Status and control points recorded for later hookup to control FSM

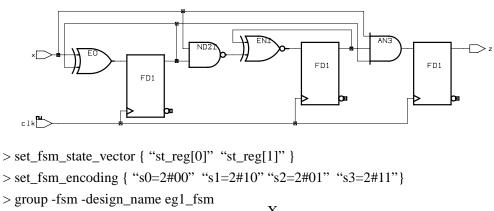

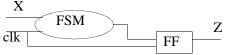

### **Control FSM**

A state graph is constructed A set of control actions is constructed Each of these drives a control point Actions are annotated on the transitions of the state graph Status points are mapped from the scheduled CDFG Netlist augmented with Control Unit (CU) Inputs to CU are status signals Outputs are connected to the control points A State Table is constructed It will serve as input to the FSM compiler

EMA1997

BEHAVIORAL COMPILER

III - 23 of 26

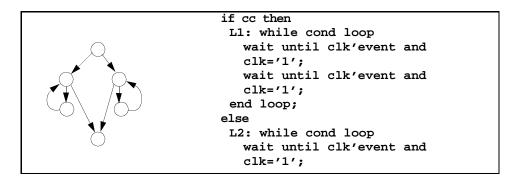

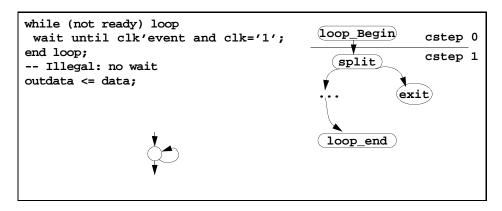

### States and csteps

#### One to one mapping except:

Loop has one more cstep than states

Mutually exclusive loops have disjoint states mapping to the same csteps

| while cond loop      | 4 |

|----------------------|---|

| wait until clk'event |   |

| and clk='1';         | Ŷ |

| end loop;            | V |

|                      |   |

### **BC** constraints on loops

Loop-end at least one cstep after loop-begin

Loop exit at least on cstep after cond. evaluation

1+ clock edges inside a loop (O not allowed)

EMA1997

BEHAVIORAL COMPILER

III - 25 of 26

### Invoking the scheduler

schedule command automatically invokes timing (if necessary), scheduling, allocation, netlisting and control unit synthesis.

bc\_shell> set\_cycles 5 -from\_begin loop1 -to\_end loop1 bc\_shell> set\_common\_resource op1 op2 -min\_count 1 bc\_shell> schedule -effort med -io\_mode super effort: zero, med, high

BC outputs

bc\_shell> report\_schedule -operations -variables bc\_shell> write -hierarchy -format vhdl -out mydesign.vhd compile -map\_effort medium optimize\_registers write -format edif -hierarchy

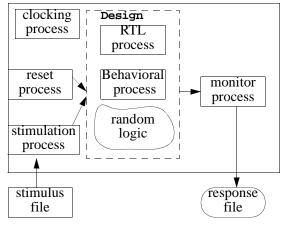

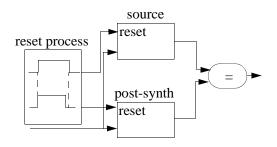

## **IV. HDL descriptions and semantics**

### **Objectives**

VHDL styles for synthesis

Overall structure of models for simulation

BC interpretation of constructs

Main feature of BC

Simulation and comparison of design before and after synthesis

Design should be tested thoroughly before synthesis

Pre-synthesis simulation faster than post-synth. simulation

⇒ Test as much as poss. at behav. level

Development of good test benches is very important

It is also very time-consuming

May be more than the development of the model itself

### **Pre-synthesis model**

#### Test bench

EMA1997

HDL descriptions and semantics

IV - 3 of 30

### The design

#### Must be represented by

A VHDL entity

An associated architecture

```

library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity design is

port (clk, reset: in std_logic;

ip: in signed (7 downto 0);

op: out signed(7 downto 0));

end design;

```

### The design (cont'd)

EMA1997

HDL descriptions and semantics

IV - 5 of 30

### **Behavioral processes**

BC schedules behavioral processes only Random logic outside processes and RTL processes preserved during scheduling Multiple behavioral processes scheduled independently No attempt by BC to maintain synchronicity User must maintain synchronicity by providing strobes, ready signals, etc. Synchronization more difficult when non-cycle-fixed I/O is present Local variables to a process are mapped to registers

Optimization based on life time

### **Behavioral processes (cont'd)**

No sensitivity list

Variables only visible within the process

```

P1: process

-- local variables

variable x: signed (7 downto 0);

...

begin

-- behavioral statements;

...

wait until clk'event and clk ='1';

end process P1;

```

EMA1997

HDL descriptions and semantics

IV - 7 of 30

### **Clock and Reset**

#### **BC** supports

A single-phase edge-triggered clock

Synchronous or asynchronous resets

#### Interpretation

Each clock edge forces the process to await the next active clock edge before proceeding

An output write may be forced to fall one cycle after another operation

User may insert any number of clock edges in the model

Edge polarities cannot be mixed inside the same process

Different processes may use different edges, clock nets, and frequencies

Sensitivity lists are not allowed in a behavioral process

Inside a behavioral process only one signal and one polarity can be the argument of any wait statement

### Synchronous resets

```

main: process

begin

reset_loop: loop

--reset tail

pc := (others => '0'); sp:= (others =>'1');

wait until clk'event and clk='1';

if reset ='1' then exit reset_loop; end if;

main_loop: loop

-- normal mode

instr := memory(pc);

wait until clk'event and clk='1';

if reset ='1' then exit reset_loop; end if;

case (instr) is

when "00100000" => ...

end loop main_loop;

end loop reset_loop;

end process main;

```

EMA1997

HDL descriptions and semantics

IV - 9 of 30

### Synchronous resets (cont'd)

| Exit statement after each clock edge                                                   |

|----------------------------------------------------------------------------------------|

| Loop encloses the entire process behavior                                              |

| Loop begins with reset specific behavior                                               |

| BC infers a reset if no reset branch is missing and all branches are identical         |

| BC reports well formed resets<br>A global synchronous reset has been inferred          |

| A reset can be included at bc_shell level<br>> set_behavioral_reset reset -active high |

| A reset net or port should be provided                                                 |

| Unused net is deleted during elaboration                                               |

| $\Rightarrow$ add a dummy port or logic which uses the reset net                       |

#### Asynchronous resets

Use set\_bahavioral\_async\_reset or

If needed for pre-synthesis simulation

Readability 🔺

```

wait until (clk'event and clk ='1')

--synopsys synthesis_off

or ( reset'event and reset ='1')

--synopsys synthesis_on

if reset ='1' then

exit reset_loop;

end if;

```

EMA1997

HDL descriptions and semantics

IV - 11 of 30

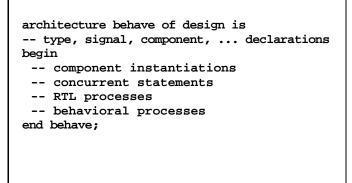

### **I/O Operations**

```

entity design is

port (clk, reset: in std_logic;

ip: in signed (7 downto 0);

op: out signed(7 downto 0));

end design;

architecture behave of design is

signal sig: signed(7 downto 0);

begin

P1: process

variable v1,v2: signed (7 downto 0);

begin

wait until clk'event and clk ='1';

v1 := ip; --read

v2:= ip; -- different read

wait until clk'event and clk ='1';

sig <= v1; -- write

wait until clk'event and clk ='1';

-- read and write

op <= v2 + sig

wait until clk'event and clk ='1';

end process P1;

end behave;

```

### **I/O Operations**

#### I/O R/W inferred from references to architecture signals or entity ports

#### Note different reads in "the same cycle"

#### Cycle stretched in 2 I/O modes

If one read wanted then re-use v1

#### **BC** registers output ports and written signals

New value appears at the next cycle Avoid "<=" except for communicating with outside

EMA1997

HDL descriptions and semantics

IV - 13 of 30

### I/O Operations (cont'd)

#### R/W signals may serve as milestones in a very complex design

Constrain the schedule

Reduce the search space

Make testing easier

#### **BC** assumes registered inputs

### **Flow of Control**

#### Most constructs supported

For, while , infinite loops If-then-elsif-else, case statements Functions, procedures

#### Next, exit

Associated with a reset, or Affect the immediate enclosing loop

EMA1997

HDL descriptions and semantics

IV - 15 of 30

### **Fixed bound FOR loops**

#### Unrolled by default at elaboration time

Eliminates hardware evaluating the conditional

Allows writing loops containing no clock statements

Allows simultaneous scheduling of operations outside the loop and operations from different iterations

#### To force keeping complex loops rolled

```

attribute dont_unroll: boolean;

attribute dont_unroll of loop_C: label is true;

...

loop_C: for i in 0 to 1000 loop ...

```

### **General loops**

#### Not unrolled

Infinite loops While loops and loops with "dynamic" range Loops with explicit conditional exit

EMA1997

HDL descriptions and semantics

IV - 17 of 30

### **Pipelined loops**

| oop                                           | $1$ $\mathbf{A}$ read $\mathbf{A}$ initiation     |

|-----------------------------------------------|---------------------------------------------------|

| a:= inputport;                                | a T 1                                             |

| <pre>wait until clk'event and clk ='1';</pre> | t op1 v interval                                  |

| b:= op1(a);                                   | e op2 read                                        |

| wait until clk'event and clk ='1';            | $n = \frac{0p3}{1} \frac{op1}{1}$                 |

| c:= op2(b);                                   | op4 op2 read                                      |

| wait until clk'event and clk ='1';            | $c = \frac{1}{0p5,w} \frac{1}{0p3} \frac{1}{0p1}$ |

| -                                             | y op4 op2 read                                    |

| d:= op3(c)                                    | $\overline{op5}, w \overline{op3} \overline{op1}$ |

| <pre>wait until clk'event and clk ='1';</pre> | op4 op2                                           |

| e:= op4(d);                                   |                                                   |

| <pre>wait until clk'event and clk ='1';</pre> | spe, spe                                          |

| <pre>outputport &lt;= op5(e);</pre>           | op4                                               |

| <pre>wait until clk'event and clk ='1';</pre> | op5,w                                             |

| and loop;                                     |                                                   |

latency: multiple of II

II=2; L=6

Throughput = 1/II = 0.5

### **Pipelined loops**

#### **Previous example hypothesis**

No chaining possible Operations so diff. they cannot share the same hardware.

#### **Before pipelining**

1/6 resource utilization

1/6 throughput

#### After pipelining

1/2 utilization

1/2 throughput

EMA1997

HDL descriptions and semantics

IV - 19 of 30

### Pipelined loops and Fixed I/O mode

```

ppl: while (cond) loop

u := inp; --read

x := x*a + u*b;

output <= transport x after 20 ns -- 2cycles

wait until clk'event and clk ='1';

end loop ppl;

wait until clk'event and clk ='1'; -- purge pipeline

wait until clk'event and clk ='1';

wait until clk'event and clk ='1';

output <= in_order_output</pre>

```

(read read read)

writ writ writ read

### Other I/O modes

Implicit declaration of a pipeline (as in fixed mode) is not possible nor necessary

> pipeline\_loop ppl -initiation 1 -latency 3

Regardless of I/O mode re-using the outputs cannot be too close to the end of the pipelined loop

No exit later than II+1 to avoid explosion of states

Rolled loops cannot be nested inside pipelined loops

BC cannot determine statically the concurrency between iterations

EMA1997

HDL descriptions and semantics

IV - 21 of 30

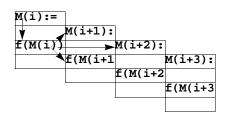

### **Memory inference**

Memories specified using arrays

Memories consist of words

BC schedules accesses and controls ports

RAM accesses are synthetic

BC makes conservative assumptions about address conflicts

An address conflict occurs: two accesses to same mem. one access is a write

| M(14) := 5;   | M(14) := 5;    |

|---------------|----------------|

| x := M(14);   | x := M(13);    |

| True conflict | False conflict |

|               |                |

BC does not distinguish between false and true conflicts

Override BC deduction:

> ignore\_memory\_precedences -from op1 to op2

### Memory code

```

architecture beh of mem_dsg is

subtype resource is integer;

attribute variables: string;

attribute map to module: string;

type mem_type is array (0 to 15) of signed(7 downto

0);

begin

behavP: process

constant Mem1: resource:=0; --physical memory

attribute variables of Mem1: constant is "M";

attribute map_to_module of Mem1: constant is

"DW03_ram1_s_d";

variable M: mem_type;

--logical memory

begin

. . .

M(12) := "00101100"; -- mem. w.

outport \leq M(2*x); -- mem. r.

```

EMA1997

HDL descriptions and semantics

IV - 23 of 30

### **Memory timing**

#### **Normal loops**

Iterations are insulated

R/W of one iteration strictly precede R/W of next iteration

#### **Pipelined** loop

Iterations co-exist  $\Rightarrow$  inter-iteration conflicts appear

These conflicts may be false

> ignore memory\_loop\_precedences {op1 op2}

### Memory timing (cont'd)

```

for (i in 0 to Msize) loop

M(i) := inport;

outport <= transport (f(M(i)) after 20 ns;

wait until clk'event and clk='1';

end loop;</pre>

```

II cannot 1 or 2 due to false memory conflict, it may be 3

EMA1997

HDL descriptions and semantics

IV - 25 of 30

### Other memory considerations

#### **RAM operations**

appear just as array references

but may be multi-cycle operations

use registers if poss.

#### Declaration of memory forgotten or misspelled $\Rightarrow$

Array of words becomes a large register

Busses used for reads

MUXes uses for writes

Area and logic optimization become impractical

#### If memory contains records

Accessing a single field means accessing the whole record

$\Rightarrow$  partition the memory in different memories

### Synthetic components

#### Component synthesized on the fly when needed

Ex: adders, multipliers ... Encapsulated in DesignWare libraries Sharable resources during allocation

#### $\neq$ modules, each module has $\neq$ implementations

adder module, add/sub module,  $\neq$  carry chain implementations

EMA1997

HDL descriptions and semantics

IV - 27 of 30

### **DesignWare developer**

Function or procedure used in more than one place

Is not in the DW lib.

Wish the hardware implementation sharable

ex: MAC op. for DSP with  $\neq$  implementations

repeated random logic modules

Define a function instead of code

| if (cond) then |

|----------------|

| x := d1;       |

| else           |

| x:=d2;         |

| end if;        |

|                |

Then use the map\_to\_module pragma

$\Rightarrow$  use DW module instead of inlining the function simplify the FSM by moving parts to Data Path

Size of the FSM exponential in number of inputs

### **Preserved functions**

#### By default, BC inlines subprograms during elaboration

To prevent inlining: function fid (...) is -- synopsys preserve\_function Inlining controlled at subpgm definition

#### Equivalent to a DW part with some restrictions

No signal R/W No sequential DW parts No clock edge statements No rolled loops No unconstrained types No multiple implementations Cannot be used in an RTL process

EMA1997

HDL descriptions and semantics

IV - 29 of 30

### **Pipelined components**

#### Comb. logic as a synth. comp. may have excessive delay.

1. Lengthen the clock cycle

Bad solution

Increases chaining while diminishing sharing

2. Allow multi-cycle operations

Latency penalty

Registered inputs

#### 3. Pipelining

May be obtained by retiming (optimize\_registers)

Some DW components are pipelined

Use DW developer

Use a directive

> set\_pipeline\_stages {op1 op2} -fixed\_stages 3

## V. I/O modes

### I/O modes

#### Three I/O modes

three different interpretations of HDL semantics

Modes define equivalence between the pre-synthesis and post-synthesis models

# Pre and post synthesis designs perform the same operation at the same time on their inputs

Very strict, rules out scheduling

#### Fixed I/O mode:

The I/O behavior is always the same

A communication protocol working with the model will work with the synthesized design

Test bench will work with both

Strict discipline, if computation two long, BC will exit with error

### I/O modes (cont'd)

#### Superstate mode

I/O operations order is preserved, time may be stretched Input and design distinguishable only by counting clock cycles Test bench preserved if independent of number of clock edges A good balance between optimization and verification

#### Free floating mode

I/O operation are freely shifted in time Allows maximum optimization Difficult verification

EMA1997

I/O modes

V - 3 of 18

### **Cycle-Fixed Mode**

#### Any scheduled mode has a fixed counterpart

A timing diagram not achievable in fixed mode

$\Rightarrow$  Not achievable in any mode

Source can talk correctly to its environment

$\Rightarrow$  Synthesized process will

Source should be written allowing BC synthesis

Without  $\pm$  any clock cycle

#### I/O timing preserved except for reset

Resets not needed in simulation

1+ cycles needed to startup the FSM in synthesized design

BC always registers the process outputs

$\Rightarrow$  1 cycle skew with simulation

### Cycle-Fixed Mode (Test bench)

Provide two reset pulses

Reset source one cycle longer

Other signals from the test bench should not transition exactly on the clock edge

Otherwise setup hold violations

EMA1997

I/O modes

V - 5 of 18

### Fixed Mode rules (Straight line code)

Source should be written allowing BC synthesis without  $\pm$  any clock cycle

BC fails if a series of operations cannot fit in the allocated time

Its decision takes into account

Chaining

Sequential operations

Multicycle operations

Manual constraints

A multicycle operation can only be chained with an output operation

Be careful about muticycle operations

Not obvious by simple inspection

Especially memory operations

# Fixed Mode rules (Loops)

Loop boundaries are not free to be rescheduled

A loop is mapped to 2+ csteps

Loop test is performed inside the cycle of the loop

$\Rightarrow$  No transition goes past the loop

$\Rightarrow$  Must be a clock edge between loop test and any succeeding output

EMA1997

I/O modes

V - 7 of 18

### Loops in fixed mode

Mental representation of a while loop

```

free_loop: loop

if ready then

wait until clk'event and clk='1';

exit free_loop;

end if;

wait until clk'event and clk='1';

end loop;

dataout <= data;</pre>

```

### Nested loops and FM

```

while (not done) loop

-- A: wait needed

while (not ready) loop

wait until clk'event and clk='1';

end loop;

--B: wait needed

end loop;

```

A: otherwise two condition must be tested in the same cycle B: otherwise one branch of nested loop without a clock edge

EMA1997

I/O modes

V - 9 of 18

### Successive loops and FM

while (not done) loop

wait until clk'event and clk='1';

end loop;

-- wait needed

while (not ready) loop

wait until clk'event and clk='1';

end loop;

### **Complex loop conditions**

Complex conditions may take more than 1 cycle while (x\*inport1 < y-inport2) ... Two reads locked to the same cycle Operations are performed: 2 cycles Extra cycle should be taken into account in the subsequent code

EMA1997

I/O modes

V - 11 of 18

### **Superstate-Fixed Mode**

#### **Properties**

Preserves the I/O ordering but

Not necessarily the number of clock edges between I/O operations

Latency of the design may change by user commands without changing the HDL > pipeline\_loop main\_loop -latency 16 -initiation 4

A superstate is the interval between 2 source clock edges.

BC is allowed to add clock edges to a superstate

#### Equivalence

Any I/O write will take place in the last cycle of the superstate  $% \mathcal{A}$

An I/O read can take place in any cycle of the superstate

# Superstate-Fixed Mode (Implications)

Any 2 writes happening in the same superstate must be simultaneous Input data must be held stable during a superstate

I/O protocols must handle extra delays possibly added by BC

$\Rightarrow$  handshaking is a candidate protocol

EMA1997

I/O modes

V - 13 of 18

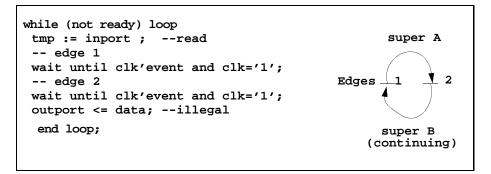

### Superstate Rules (continuing superstate)

The first superstate of a loop contains any I/O

$\Rightarrow$  no superstate containing a loop continue may contain an I/O write

### Superstate Rules (separating write orders)

There must be a clock edge between a write and the beginning of a loop whose first superstate contains a write operation

```

this_port <= some;

-- must have a wait

loop

that_port <= any ;

wait until clk'event and clk='1';

end loop;

```

Ex: 1st superstate starts outside of the loop

$\Rightarrow$  outside write has to migrate inside the loop (contradiction)

EMA1997

I/O modes

V - 15 of 18

### Superstate Rules (Conditional superstate)

A write can never precede a conditional superstate boundary if any I/O operation succeeds the boundary

thisport <= some; -- must have a wait while strobe loop wait until clk'event and clk='1'; end loop; reg1 := thatport;

### **Superstate Rules** (Escaping from the loop)

No I/O write can occur between the exit and the last clock edge before the exit

busy: while strobe loop wait until clk'event and clk='1'; thisport <= some; if (interrupt) then exit busy; end if; end loop;

EMA1997

I/O modes

V - 17 of 18

### **Free-Floating Mode**

I/O operations are free to float with respect to one another

Operations on single port are partially ordered

Series of reads can be permuted

No ordering between operations on different ports

Data precedences and constraints respected

Deleting or adding clock edges permitted

If two signals are logically bound then express it using manual constraints

## **VI. Explicit Directives and Constraints**

### Labeling (Default naming)

If "+" falls in line 35 the default name is

P1/outloop/innerloop/add\_35

If > one "+" then add\_35\_1, add\_35\_2

Default names created for unlabeled loops

If unrolled loop: add\_35\_i\_3 for iteration 3

> find -hier cell > names.txt

Drawback: cell names change if source edited

```

P1: process

outloop: loop

innerloop: loop

x := a+b;

end loop;

end loop;

end process;

```

### Labeling (user naming)

#### Use pragma

New name not sensitive to editing is

P1/outloop/innerloop/alu

Limitations

Ambiguity when many operations on the same line,

Not applicable to I/O and memory operations loop boundaries

x := a+b; -- synopsys label alu

...

EMA1997

Explicit Directives and Constraints

VI - 3 of 9

### Labeling (improved naming)

#### Labeling lines

P1/outloop/innerloop/add\_thisline

If multiple operation: names generated from left to right

```

...

x := a+b; -- synopsys line_label thisline

...

```

### **Scheduling Constraints**

> preschedule p2/res\_loop/main/sub\_107 4

Forces the named operation into a particular cstep

The cstep is relative to the beginning of the enclosing hierarchical context

sub\_107 will be put in the 5th cstep of loop main

> set\_cycles 3 -from op1 -to op2

op2 must start exactly 3 cycles after op2 started

> set\_cycles 3 -from\_begin loop4 -to\_end loop4

> set\_min\_cycles 5 -from\_end loop4 -to\_begin loop6

EMA1997

Explicit Directives and Constraints

VI - 5 of 9

# Scheduling Constraints (cont'd)

chain\_operations equivalent to set\_cycles 0 dont\_chain\_operations equivalent to set\_min\_cycles 1 remove\_scheduling\_constraints removes all explicit constraints

> set\_common\_resource op1 op2 op3 -min\_count 2

### **Shell Variables**

> bc\_enable\_chaining = false Globally turns off chaining of synthetic operations. Use more specific constraints. true by default

bc\_enable\_multi\_cycle: true by default

bc\_enable\_speculative\_execution: false by default

EMA1997

Explicit Directives and Constraints

VI - 7 of 9

### Shell Variables (cont'd)

bc\_fsm\_coding\_style

one\_hot

counter\_style

two\_hot

use\_fsm\_compiler (default)

reset\_clears\_all\_bc\_registers when set to true Clear pins of all registers connected to the reset net With set\_behavioral\_async\_reset provides asynch reset to all registers

### **Shell Commands**

set\_margin controls the margin allowed for control and muxing delays when timing the design before scheduling

> register\_control -inputs -outputs

Forces registers on inputs and/or outputs of the control FSM

May improve the cycle time but

May increase latency if conditionals on the critical path

set\_stall\_pin Used to stop the design for some external event to occur Equivalent to a gated clock

EMA1997

Explicit Directives and Constraints

VI - 9 of 9

# VII. RTL Design Methodology

#### **RTL Design flow** 1 (Functional specs Behav. coding Behavioral RTL coding 2 RTL code RTL simulation 3 4 Logic synthesis 5 Test insertion Netlist simulation 6 Floorplanner 7 Place and Route 8

## **RTL Design flow**

#### It is an iterative process

If simulation not satisfactory, goto RTL code

If timing requirements of the clock not met after synthesis

• modify code

$\bullet change \ synthesis \ strategy$

•hack the netlist

#### After P&R

Back-annotate real delay values

Perform in place optimization to meet routing delays

EMA1997

RTL Design Methodology

VII - 3 of 21

## **Design refinement**

Block diagram of ASIC created after step 1 HDL coding of each block Style of coding important for synthesis Knowledge internals ⇒ write good synth. code Hierarchy based on func. specs. ⇒ critical path may traverse hierarchy boundaries Best results when critical path in one block Ensure registered output blocks ⇒ avoid complicated timing budgeting

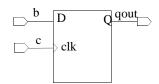

## HDL FF Code

entity comp is

port (b, c: in bit; qout: out bit);

end comp;

architecture FF of comp is

begin

P1: process

begin

wait until c'event and c ='1';

qout <= b;

end process P1;

end FF;</pre>

EMA1997

RTL Design Methodology

VII - 5 of 21

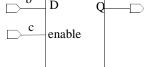

## **HDL latch Code**

## HDL AND Code

```

entity comp is

port (b, c: in bit; qout: out bit);

end comp;

architecture and2 of comp is

begin

P1: process (b, c)

begin

if (c ='1') then qout <= b;

else qout <= '0';

end if;

end process P1;

end and2;</pre>

```

EMA1997

RTL Design Methodology

VII - 7 of 21

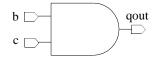

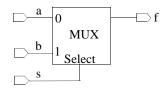

## **MUX inference**

Often gates are inferred instead of MUXes

map\_to\_entity pragma forces mapping to MUXes or

Function calls or

Instantiating MUXes from Synopsys generic library (gtech.db) and assigning map\_only attribute

## **MUX modeling**

```

entity comp is

port (a,b, s: in bit; f: out bit);

end comp;

architecture mux of comp is

begin

P1: process (a,b, s)

begin

case s is

when '0' => f<=a;

when '1' => f<=b;

end case;

end process P1;

end mux;</pre>

```

EMA1997

RTL Design Methodology

VII - 9 of 21

## Synthesized gate-level netlist simulation

VHDL simulation models of technology library cells

#### **Unit Delay Structural Model (UDSM)**

Comb. cells delay = 1ns Seq. cells delay = 2ns

#### Full-Timing Structural Model (FTSM)

Transport wire delays Pin-to-pin delays Zero delays functional networks Timing constraints violations reported as warnings

## Netlist simulation (cont'd)

#### Full-Timing Behavioral Model (FTBM)

Transport wire delays Pin-to-pin delays Very detailed timing verification

#### Full-Timing optimized Gate-level Model (FTGM)

Transport wire delays Pin-to-pin delays Warnings + handling X values Timing constraints violations reported as warnings

#### Logic synthesis

Transform RTL HDL to gates Optimize by selecting the optimal combination of technology library cells

EMA1997

RTL Design Methodology

VII - 11 of 21

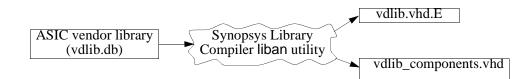

## Simulation of commercial ASICs

vdlib.vhd.E : encrypted, contains simulation models with timing delays vdlib\_components.vhd: package, declarations for all the cells of ASIC vendor library